# 3 Phase Switching Amplifier

## **FEATURES**

- Low Cost 3 Phase Intelligent Switching Amplifier

- ◆ Directly Connects to Most Embedded Microcontrollers and Digital Signal Controllers

- ◆ Integrated Gate Driver Logic with Dead-Time Generation and Shoot-through Prevention

- ♦ Wide Power Supply Range (8.5V To 60V)

- ♦ Over 10A Peak Output Current per Phase

- ◆ Independent Current Sensing for each Output

- ◆ User Programmable Cycle-by-cycle Current Limit Protection

- Over-Current and Over-Temperature Warning Signals

# **APPLICATIONS**

- ♦ 3 phase brushless DC motors

- ♦ Multiple DC brush motors

- ♦ 3 independent solenoid actuators

# **DESCRIPTION**

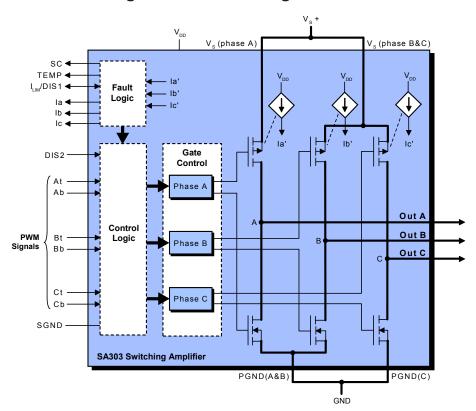

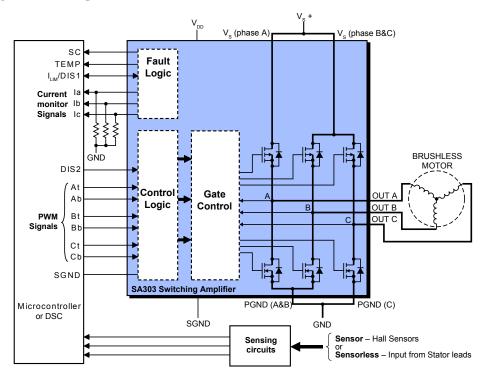

The SA303 is a fully integrated switching amplifier designed primarily to drive three-phase Brushless DC (BLDC) motors. Three independent half bridges provide over 10 amperes peak output current under microcontroller or DSC control. Thermal and short circuit monitoring is provided, which generates fault signals for the microcontroller to take appropriate action. A block diagram is provided in Figure 1.

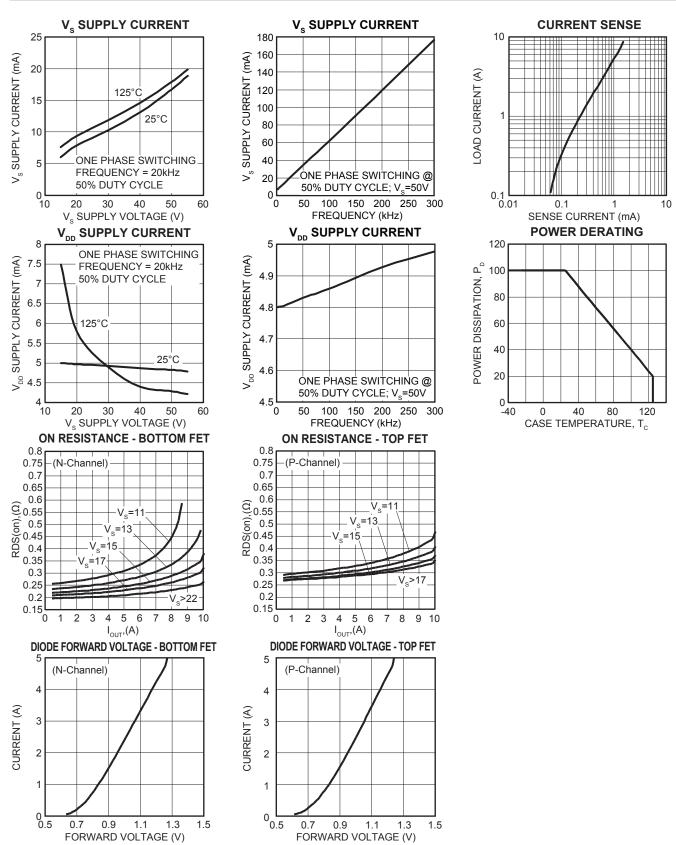

Additionally, cycle-by-cycle current limit offers user programmable hardware protection independent of the microcontroller. Output current is measured using an innovative low loss technique. The SA303 is built using a multi-technology process allowing CMOS logic control and complementary DMOS output power devices on the same IC. Use of P-channel high side FETs enables 60V operation without bootstrap or charge pump circuitry.

The HSOP surface mount package balances excellent thermal performance with the advantages of a low profile surface mount package.

Figure 1. BLOCK Diagram

# 1. Characteristics and Specifications

# **Absolute Maximum Ratings**

| Parameter                             | Symbol           | Min    | Max                    | Units |

|---------------------------------------|------------------|--------|------------------------|-------|

| SUPPLY VOLTAGE                        | $V_s$            |        | 60                     | V     |

| SUPPLY VOLTAGE                        | $V_{_{ m DD}}$   |        | 5.5                    | V     |

| LOGIC INPUT VOLTAGE                   |                  | (-0.5) | (V <sub>DD</sub> +0.5) | V     |

| OUTPUT CURRENT, peak, 10ms (Note 2)   | I <sub>OUT</sub> |        | 10                     | Α     |

| POWER DISSIPATION, avg, 25°C (Note 2) | $P_{_{D}}$       |        | 100                    | W     |

| TEMPERATURE, solder, 10sec            | T <sub>s</sub>   |        | 260                    | °C    |

| TEMPERATURE, junction (Note 2)        | $T_{J}$          |        | 150                    | °C    |

| TEMPERATURE RANGE, storage            | T <sub>STG</sub> | -65    | 125                    | °C    |

| OPERATING TEMPERATURE, case           | T <sub>A</sub>   | -25    | 85                     | °C    |

# **Specifications**

| Parameter                                         | Test Conditions (Note 1)                                                          | Min  | Тур  | Max | Units |

|---------------------------------------------------|-----------------------------------------------------------------------------------|------|------|-----|-------|

| LOGIC                                             |                                                                                   |      |      |     |       |

| INPUT LOW                                         |                                                                                   |      |      | 1   | V     |

| INPUT HIGH                                        |                                                                                   | 1.8  |      |     | V     |

| OUTPUT LOW                                        |                                                                                   |      |      | 0.3 | V     |

| OUTPUT HIGH                                       |                                                                                   | 3.7  |      |     | V     |

| OUTPUT CURRENT (SC, Temp, I <sub>LIM</sub> /DIS1) |                                                                                   |      | 50   |     | mA    |

| POWER SUPPLY                                      |                                                                                   |      |      |     |       |

| $V_s$                                             |                                                                                   | UVLO | 50   | 60  | V     |

| V <sub>s</sub> UNDERVOLTAGE LOCKOUT, (UVLO)       |                                                                                   |      | 8.3  |     | V     |

| $V_{DD}$                                          |                                                                                   | 4.5  |      | 5.5 | V     |

| SUPPLY CURRENT, V <sub>S</sub>                    | 20 kHz (One phase switching at 50% duty cycle) , $\rm V_S$ =50V, $\rm V_{DD}$ =5V |      | 25   | 30  | mA    |

| SUPPLY CURRENT, V <sub>DD</sub>                   | 20 kHz (One phase switching at 50% duty cycle) , $V_s$ =50V, $V_{DD}$ =5.5V       |      | 5    | 6.5 | mA    |

| CURRENT LIMIT                                     |                                                                                   |      |      |     |       |

| CURRENT LIMIT THRESHOLD (Vth)                     |                                                                                   |      | 3.75 |     | V     |

| Vth HYSTERESIS                                    |                                                                                   |      | 100  |     | mV    |

| OUTPUT                                            |                                                                                   |      |      |     |       |

| CURRENT, CONTINUOUS                               | 25°C Case Temperature                                                             | 3    |      |     | Α     |

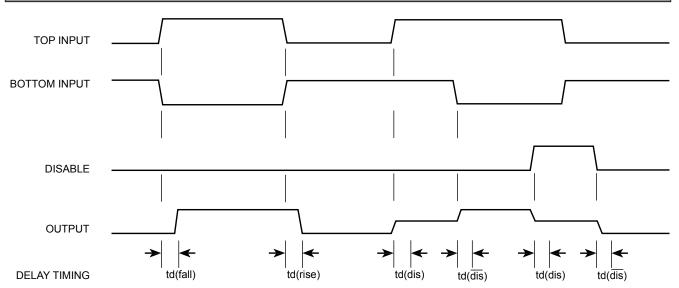

| RISING DELAY, TD(RISE)                            | See Figure 10                                                                     |      | 270  |     | ns    |

| FALLING DELAY, TD(FALL)                           | See Figure 10                                                                     |      | 270  |     | ns    |

| DISABLE DELAY, TD(DIS)                            | See Figure 10                                                                     |      | 200  |     | ns    |

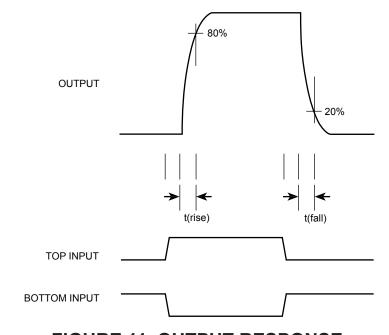

| ENABLE DELAY, TD(DIS)                             | See Figure 11                                                                     |      | 200  |     | ns    |

| RISE TIME, T(RISE)                                | See Figure 11                                                                     |      | 50   |     | ns    |

| FALL TIME, T(FALL)                                |                                                                                   |      | 50   |     | ns    |

| ON RESISTANCE SOURCING (P-CHANNEL)                | 3A Load                                                                           |      | 400  |     | mΩ    |

| ON RESISTANCE<br>SINKING (N-CHANNEL)              | 3A Load                                                                           |      | 400  |     | mΩ    |

# Specifications, continued

| Parameter                    | Test Conditions (Note 1) | Min | Тур  | Max | Units |

|------------------------------|--------------------------|-----|------|-----|-------|

| THERMAL                      |                          |     |      |     |       |

| THERMAL WARNING              |                          |     | 135  |     | °C    |

| THERMAL WARNING HYSTERESIS   |                          |     | 40   |     | °C/W  |

| RESISTANCE, junction to case | Full temperature range   |     | 1.25 | 1.5 | °C/W  |

| TEMPERATURE RANGE, case      | Meets Specifications     | -25 |      | +85 | °C    |

#### NOTES:

- 1. (All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical performance characteristics and specifications are derived from measurements taken at typical supply voltages and  $T_c = 25^{\circ}C$ ).

- 2. Long term operation at elevated temperature will result in reduced product life. De-rate internal power dissipation to achieve high MTBF.

- 3. Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any set of conditions, do not exceed the specified current rating or a junction temperature of 150°C.

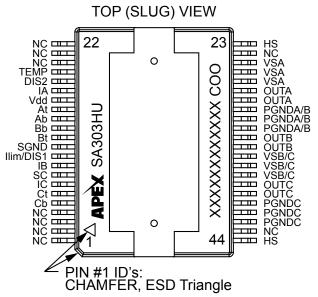

Figure 2. 44-Pin HSOP Slug-Up, Package Style HU

Figure 3. External Connections - 44-Pin HSOP

| Table 1. Pin Descriptions - 44-Pin HSOP |                                                               |                    |                                                                                                                                                                                                                                                   |  |  |

|-----------------------------------------|---------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin #                                   | Pin Name                                                      | Signal Type        | Simplified Pin Description                                                                                                                                                                                                                        |  |  |

| 25,26,27                                | V <sub>s</sub> (phase A)                                      | Power              | High Voltage Supply (8.5-60V) supplies phase A only                                                                                                                                                                                               |  |  |

| 38,39                                   | OUT C                                                         | Power Output       | Half Bridge C Power Output                                                                                                                                                                                                                        |  |  |

| 40,41,42                                | PGND (phase C) Power High Current GND Return Path for Power C |                    | High Current GND Return Path for Power Output C                                                                                                                                                                                                   |  |  |

| 8                                       | SC                                                            | Logic Output       | Indication of a short of an output to supply, GND or another phase                                                                                                                                                                                |  |  |

| 4                                       | Cb                                                            | Logic Input        | Logic high commands C phase lower FET to turn on                                                                                                                                                                                                  |  |  |

| 5                                       | Ct                                                            | Logic Input        | Logic high commands C phase upper FET to turn on                                                                                                                                                                                                  |  |  |

| 6                                       | IC                                                            | Analog Output      | Phase C current sense output                                                                                                                                                                                                                      |  |  |

| 8                                       | IB                                                            | Analog Output      | Phase B current sense output                                                                                                                                                                                                                      |  |  |

| 10                                      | I <sub>LIM</sub> /DIS1                                        | Logic Input/Output | As an output, logic high indicates cycle-by-cycle current limit, and logic low indicates normal operation. As an input, logic high places all outputs in a high impedance state and logic low disables the cycle-by-cycle current limit function. |  |  |

| 11                                      | SGND                                                          | Power              | Analog and digital GND – internally connected to PGND                                                                                                                                                                                             |  |  |

| 12                                      | Bt                                                            | Logic Input        | Logic high commands B phase upper FET to turn on                                                                                                                                                                                                  |  |  |

| 13                                      | Bb                                                            | Logic Input        | Logic high commands B phase lower FET to turn on                                                                                                                                                                                                  |  |  |

| 14                                      | Ab                                                            | Logic Input        | Logic high commands A phase lower FET to turn on                                                                                                                                                                                                  |  |  |

| 15                                      | At                                                            | Logic Input        | Logic high commands A phase upper FET to turn on                                                                                                                                                                                                  |  |  |

| 16                                      | V <sub>DD</sub>                                               | Power              | Logic Supply (5V)                                                                                                                                                                                                                                 |  |  |

| 17                                      | IA                                                            | Analog Output      | Phase A current sense output                                                                                                                                                                                                                      |  |  |

| 18                                      | DIS2                                                          | Logic Input        | Logic high places all outputs in a high impedance state                                                                                                                                                                                           |  |  |

| 19                                      | TEMP                                                          | Logic Output       | Thermal indication of die temperature above 135°C                                                                                                                                                                                                 |  |  |

| 33,34                                   | OUT B                                                         | Power Output       | Half Bridge B Power Output                                                                                                                                                                                                                        |  |  |

| 35,36,37                                | V <sub>s</sub> (phase B&C)                                    | Power              | High Voltage Supply phase B & C                                                                                                                                                                                                                   |  |  |

| 28,29                                   | OUT A                                                         | Power Output       | Half Bridge A Power Output                                                                                                                                                                                                                        |  |  |

| 30,31,32                                | PGND (phase A&B)                                              | Power              | High Current GND Return Path for Power Outputs A & B                                                                                                                                                                                              |  |  |

| 23,44                                   | HS                                                            | Mechanical         | Pins connected to the package heat slug                                                                                                                                                                                                           |  |  |

| 1,2,3,4,20,<br>21,22,24,43              | NC                                                            |                    | Do Not Connect                                                                                                                                                                                                                                    |  |  |

# 1.2 Pin Descriptions

- V<sub>s</sub>:Supply voltage for the output transistors. These pins require decoupling (1μF capacitor with good high frequency characteristics is recommended) to the PGND pins. The decoupling capacitor should be located as close to the V<sub>s</sub> and PGND pins as possible. Additional capacitance will be required at the V<sub>s</sub> pins to handle load current peaks and potential motor regeneration. Refer to the applications section of this datasheet for additional discussion regarding bypass capacitor selection. Note that V<sub>s</sub> (phase A) carry only the phase A supply current. V<sub>s</sub> (phase B&C) carry supply current for phases B & C. Phase A may be operated at a different supply voltage from phases B & C. Both V<sub>s</sub> voltages are monitored for undervoltage conditions.

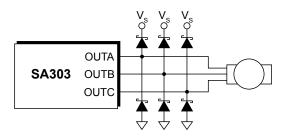

- **OUT A, OUT B, OUT C:** These pins are the power output connections to the load. NOTE: When driving an inductive load, it is recommended that two Schottky diodes with good switching characteristics (fast t<sub>RR</sub> specs) be connected to each pin so that they are in parallel with the parasitic back-body diodes of the output FETs. (See Section 2.6)

- **PGND:** Power Ground. This is the ground return connection for the output FETs. Return current from the load flows through these pins. PGND is internally connected to SGND through a resistance of a few ohms. See section 2.1 of this datasheet for more details.

- SC: Short Circuit output. If a condition is detected on any output which is not in accordance with the input commands, this indicates a short circuit condition and the SC pin goes high. The SC signal is blanked for approximately 200ns during switching transitions but in high current applications, short glitches may appear on the SC pin. A high state on the SC output will not automatically disable the device. The SC pin includes an internal  $12k\Omega$  series resistor.

- **Ab, Bb, Cb:** These Schmitt triggered logic level inputs are responsible for turning the associated bottom, or lower N-channel output FETs on and off. Logic high turns the bottom N-channel FET on, and a logic low turns the low side N-channel FET off. If Ab, Bb, or Cb is high at the same time that a corresponding At, Bt, or Ct input is high, protection circuitry will turn off both FETs in order to prevent shoot-through on that output phase. Protection circuitry also includes a dead-time generator, which inserts dead time in the outputs in the case of simultaneous switching of the top and bottom input signals.

- At, Bt, Ct: These Schmitt triggered logic level inputs are responsible for turning the associated top side, or upper P-channel FET outputs on and off. Logic high turns the top P-channel FET on, and a logic low turns the top P-channel FET off.

- Ia, Ib, Ic: Current sense pins. The SA303 supplies a positive current to these pins which is proportional to the current flowing through the top side P-channel FET for that phase. Commutating currents flowing through the backbody diode of the P-channel FET or through external Schottky diodes are not registered on the current sense pins. Nor do currents flowing through the low side N-channel FET, in either direction, register at the current sense pins. A resistor connected from a current sense pin to SGND creates a voltage signal representation of the phase current that can be monitored with ADC inputs of a processor or external circuitry.

- The current sense pins are also internally compared with the current limit threshold voltage reference, Vth. If the voltage on any current sense pin exceeds Vth, the cycle by cycle current limit circuit engages. Details of this functionality are described in the applications section of this datasheet.

- **I**<sub>LIM</sub>/**DIS1**: This pin is directly connected to the disable circuitry of the SA303. Pulling this pin to logic high places OUT A, OUT B, and OUT C in a high impedance state. This pin is also connected internally to the output of the current limit latch through a 12kΩ resistor and can be monitored to observe the function of the cycle-by-cycle current limit feature. Pulling this pin to a logic low effectively disables the cycle-by-cycle current limit feature.

- **SGND:** This is the ground return connection for the V<sub>DD</sub> logic power supply pin. All internal analog and logic circuitry is referenced to this pin. PGND is internally connected to GND through a resistance of a few ohms,. However, it is highly recommended to connect the GND pin to the PGND pins externally as close to the device as possible. Failure do to this may result in oscillations on the output pins during rising or falling edges.

- **VDD:** This is the connection for the 5V power supply, and provides power for the logic and analog circuitry in the SA303. This pin requires decoupling (at least 0.1µF capacitor with good high frequency characteristics is recommended) to the SGND pin.

- **DIS2**: The DIS2 pin is a Schmitt triggered logic level input that places OUT A, OUT B, and OUT C in a high impedance state when pulled high. DIS2 has an internal  $12k\Omega$  pull-down resistor and may therefore be left unconnected.

**TEMP:** This logic level output goes high when the die temperature of the SA303 reaches approximately 135°C. This pin WILL NOT automatically disable the device. The TEMP pin includes a  $12k\Omega$  series resistor.

**HS:** These pins are internally connected to the thermal slug on the reverse of the package. They should be connected to GND. Neither the heat slug nor these pins should be used to carry high current.

NC: These "no-connect" pins should be left unconnected.

## 2. SA303 OPERATION

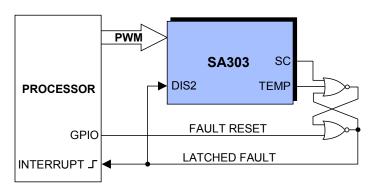

The SA303 is designed primarily to drive three phase motors. However, it can be used for any application requiring three high current outputs. The signal set of the SA303 is designed specifically to interface with a DSP or microcontroller. A typical system block diagram is shown in the figure below. Over-temperature, Short-Circuit and Current Limit fault signals provide important feedback to the system controller which can safely disable the output drivers in the presence of a fault condition. High side current monitors for all three phases provide performance information which can be used to regulate or limit torque.

Figure 4. System Diagram

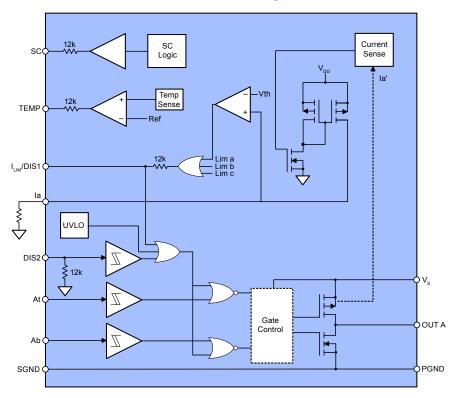

The block diagram in Figure 5 illustrates the features of the input and output structures of the SA303. For simplicity, a single phase is shown.

Figure 5. Input and output structures for a single phase

| T          | TABLE 2. TRUTH TABLE |                   |                        |      |                                |                                                                                                                                                                |

|------------|----------------------|-------------------|------------------------|------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| At, Bt, Ct | Ab, Bb, Cb           | la, lb, lc        | I <sub>LIM</sub> /DIS1 | DIS2 | OUTA,<br>OUTB,<br>OUTC         | Comments                                                                                                                                                       |

| 0          | 0                    | Χ                 | Χ                      | Χ    | High-Z                         | Top and Bottom output FETs for that phase are turned off.                                                                                                      |

| 0          | 1                    | <v<sub>th</v<sub> | 0                      | 0    | PGND                           | Bottom output FET for that phase is turned on.                                                                                                                 |

| 1          | 0                    | <v<sub>th</v<sub> | 0                      | 0    | VS                             | Top output FET for that phase is turned on.                                                                                                                    |

| 1          | 1                    | Χ                 | Χ                      | Χ    | High-Z                         | Both output FETs for that phase are turned off.                                                                                                                |

| X          | Χ                    | >V <sub>th</sub>  | 1                      | X    | High-Z                         | Voltage on Ia, Ib, or Ic has exceeded Vth, which causes I <sub>LIM</sub> /DIS1 to go high. This internally disables Top and Bottom output FETs for ALL phases. |

| Χ          | Χ                    | Χ                 | Χ                      | 1    | High-Z                         | DIS2 pin pulled high, which disables all outputs.                                                                                                              |

| X          | X                    | Х                 | Pulled<br>High         | X    | High-Z                         | Pulling the $I_{\rm LIM}$ /DIS1 pin high externally acts as a second disable input, which disables ALL output FETs.                                            |

| X          | X                    | X                 | Pulled<br>Low          | 0    | Determined<br>by PWM<br>inputs | Pulling the DIS2 pin low externally disables the cycle-by-cycle current limit function. The state of the outputs is strictly a function of the PWM inputs.     |

| Χ          | Χ                    | Χ                 | Х                      | Χ    | High-Z                         | If $V_s$ is below the UVLO threshold all output FETs will be disabled.                                                                                         |

#### 2.1 LAYOUT CONSIDERATIONS

Output traces carry signals with very high dV/dt and dl/dt. Proper routing and adequate power supply bypassing ensures normal operation. Poor routing and bypassing can cause erratic and low efficiency operation as well as ringing at the outputs.

The  $V_s$  supply should be bypassed with a surface mount ceramic capacitor mounted as close as possible to the  $V_s$  pins. Total inductance of the routing from the capacitor to the  $V_s$  and GND pins must be kept to a minimum to prevent noise from contaminating the logic control signals. A low ESR capacitor of at least  $25\mu F$  per ampere of output current should be placed near the SA303 as well. Capacitor types rated for switching applications are the only types that should be considered. Note that phases B & C share a  $V_s$  connection and the bypass recommendation should reflect the sum of B & C phase current.

The bypassing requirements of the  $V_{DD}$  supply are less stringent, but still necessary. A 0.1 $\mu$ F to 0.47 $\mu$ F surface mount ceramic capacitor (X7R or NPO) connected directly to the  $V_{DD}$  pin is sufficient.

SGND and PGND pins are connected internally. However, these pins must be connected externally in such a way that there is no motor current flowing in the logic and signal ground traces as parasitic resistances in the small signal routing can develop sufficient voltage drops to erroneously trigger input transitions. Alternatively, a ground plane may be separated into power and logic sections connected by a pair of back to back Schottky diodes. This isolates noise between signal and power ground traces and prevents high currents from passing between the plane sections.

Unused area on the top and bottom PCB planes should be filled with solid or hatched copper to minimize inductive coupling between signals. The copper fill may be left unconnected, although a ground plane is recommended.

#### 2.2 FAULT INDICATIONS

In the case of either an over-temperature or short circuit fault, the SA303 will take no action to disable the outputs.

Instead, the SC and TEMP signals are provided to an external controller, where a determination can be made regarding the appropriate course of action. In most cases, the SC pin would be connected to a FAULT input on the processor, which would immediately disable its PWM outputs. The TEMP fault does not require such an immediate response, and would typically be connected to a GPIO, or Keyboard Interrupt pin of the processor. In this case, the processor would recognize the condition as an external inter-

Figure 6. External Fault Latch Circuit

rupt, which could be processed in software via an Interrupt Service Routine. The processor could optionally bring all inputs low, or assert a high level to either of the disable inputs on the SA303.

Figure 6 shows an external SR flip-flop which provides a hard wired shutdown of all outputs in response to a fault indication. An SC or TEMP fault sets the latch, pulling the disable pin high. The processor clears the latched condition with a GPIO. This circuit can be used in safety critical applications to remove software from the fault-shutdown loop, or simply to reduce processor overhead.

In applications which may not have available GPIO, the TEMP pin may be externally connected to the adjacent DIS1 pin. If the device temperature reaches ~135°C all outputs will be disabled, de-energizing the motor. The SA303 will re-energize the motor when the device temperature falls below approximately 95°C. The TEMP pin hysteresis is wide to reduce the likelihood of thermal oscillations which can greatly reduce the life of the device.

### 2.3 UNDER-VOLTAGE LOCKOUT

The undervoltage lockout condition results in the SA303 unilaterally disabling all output FETs until  $V_{\rm S}$  is above the UVLO threshold indicated in the spec table. There is no external signal indicating that an undervoltage lock out condition is in progress. The SA303 has two  $V_{\rm S}$  connections: one for phase A, and another for phases B & C. The supply voltages on these pins need not be the same, but the UVLO will engage if either is below the threshold. Hysteresis on the UVLO circuit prevents oscillations with typical power supply variations.

# 2.4 CURRENT SENSE

External power shunt resistors are not required with the SA303. Forward current in each top, Pchannel output FET is measured and mirrored to the respective current sense output pin, Ia, Ib and Ic. By connecting a resistor between each current sense pin and a reference, such as ground, a voltage develops across the resistor that is proportional to the output current for that phase. An ADC can monitor the voltages on these resistors for protection or for closed loop torque control in some application configurations. The current sense pins source current from the V<sub>DD</sub> supply. Headroom required for the current sense circuit is approximately .5V. The nominal scale factor for each proportional output current is shown in the typical performance plot on page 4 of this datasheet.

### 2.5 CYCLE-BY-CYCLE CURRENT LIMIT

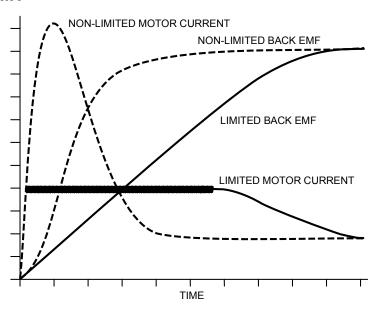

In applications where the current in the motor is not directly controlled, both the average current rating of the motor and the inrush current must be considered when selecting a proper amplifier. For example, a 1A continuous motor might require a drive amplifier that can deliver well over 10A peak in order to survive the inrush condition at startup. Because the output current of each upper output FET is measured, the SA303 is able to provide a very robust current limit scheme. This enables the SA303 to safely and easily drive virtually any brushless motor through a startup inrush condition. With limited current, the starting torque and acceleration are also limited. The plot in Figure 7 shows starting current and back EMF with and without current limit enabled.

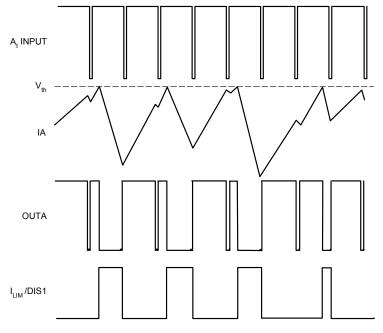

If the voltage of any of the three current sense pins exceeds the current limit threshold voltage (Vth), all outputs are disabled. After all current sense pins fall below the Vth threshold voltage AND the offending phase's top side input goes low, the output stage will return to an active state on the rising edge of ANY top side input command signal (At, Bt, or Ct). With most commutation schemes, the current limit will reset each pwm cycle. This scheme regulates the peak current in each phase during each pwm cycle as illustrated in the timing diagram below. The ratio of average to peak current depends on the inductance of the motor winding, the back EMF developed in the motor, and the width of the pulse.

Figure 8 illustrates the current limit trigger and reset sequence. Current limit engages and I<sub>LIM</sub>/DIS1 goes high when any current sense pin exceeds Vth. Notice that the moment at which the current sense signal exceeds the Vth threshold is asynchronous with respect to the input PWM signal. The difference between the PWM period and the motor winding L/R time constant will often result in an audible beat frequency sometimes called a sub-cycle oscillation.

Figure 7. Start-up Voltage and Current

FIGURE 8. CURRENT LIMIT WAVEFORMS

This oscillation can be seen on the I<sub>LIM</sub>/DIS1 pin waveform in Figure 8. Input signals commanding 0% or 100% duty cycle may be incompatible with the current limit feature due to the absence of rising edges of At, Bt, and Ct except when commutating phases. At high RPM, this may result in poor performance. At low RPM, the motor may stall if the current limit trips and the motor current reaches zero without a commutation edge which will typically reset the current limit latch.

The current limit feature may be disabled by tying the  $I_{LIM}/DIS1$  pin to GND. The current sense pins will continue to provide top FET output current information.

Typically, the current sense pins source current into grounded resistors which provide voltages to the current limit comparators. If instead the current limit resistors are connected to a voltage output DAC, the current limit can be controlled dynamically from the system controller. This technique essentially reduces the current limit threshold voltage to (Vth-VDAC). During expected conditions of high torque demand, such as start-up or reversal, the DAC can adjust the current limit dynamically to allow periods of high current. In normal operation when low current is expected, the DAC output voltage can increase, reducing the current limit setting to provide more conservative fault protection.

### 2.6 EXTERNAL FLYBACK DIODES

External fly-back diodes will offer superior reverse recovery characteristics and lower forward voltage drop than the internal backbody diodes. In high current applications, external flyback diodes can reduce power dissipation and heating during commutation of the motor current. Reverse recovery time and capacitance are the most important parameters to consider when selecting these diodes. Ultra-fast rectifiers offer better reverse recovery time and Schottky diodes typically have low capacitance. Individual application requirements will be the guide when determining the need for these diodes and for selecting the component which is most suitable.

FIGURE 9. SCHOTTKY DIODES

### 3. POWER DISSIPATION

The thermally enhanced package of the SA303 allows several options for managing the power dissipated in the three output stages. Power dissipation in traditional PWM applications is a combination of output power dissipation and switching losses. Output power dissipation depends on the quadrant of operation and whether external flyback diodes are used to carry the reverse or commutating currents. Switching losses are dependent on the frequency of the PWM cycle as described in the typical performance graphs.

**FIGURE 10. TIMING DIAGRAMS**

**FIGURE 11. OUTPUT RESPONSE**

# 4. ORDERING AND PRODUCT STATUS INFORMATION

| MODEL   | TEMPERATURE | PACKAGE                                           | PRODUCTION STATUS |

|---------|-------------|---------------------------------------------------|-------------------|

| SA303HU | -25 to 85°C | 44 pin Power SOP, Slug Up<br>(HU package drawing) | Samples Available |

# **NEED TECHNICAL HELP? CONTACT APEX SUPPORT!**

For all Apex Microtechnology product questions and inquiries, call toll free 800-546-2739 in North America. For inquiries via email, please contact apex.support@apexanalog.com.

International customers can also request support by contacting their local Apex Microtechnology Sales Representative. To find the one nearest to you, go to www.apexanalog.com

#### IMPORTANT NOTICE

Apex Microtechnology, Inc. has made every effort to insure the accuracy of the content contained in this document. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (expressed or implied). Apex Microtechnology reserves the right to make changes without further notice to any specifications or products mentioned herein to improve reliability. This document is the property of Apex Microtechnology and by furnishing this information, Apex Microtechnology grants no license, expressed or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Apex Microtechnology owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Apex Microtechnology integrated circuits or other products of Apex Microtechnology. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

APEX MICROTECHNOLOGY PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN PRODUCTS USED FOR LIFE SUPPORT, AUTOMOTIVE SAFETY, SECURITY DEVICES, OR OTHER CRITICAL APPLICATIONS. PRODUCTS IN SUCH APPLICATIONS ARE UNDERSTOOD TO BE FULLY AT THE CUSTOMER OR THE CUSTOMER'S RISK.

Apex Microtechnology, Apex and Apex Precision Power are trademarks of Apex Microtechnolgy, Inc. All other corporate names noted herein may be trademarks of their respective holders.