. . eescale Semiconductor

Technical Data

Document Number: MML09231H Rev. 1, 9/2014

## **√**RoHS

# Enhancement Mode pHEMT Technology (E-pHEMT)

# Low Noise Amplifier

The MML09231H is a single-stage low noise amplifier (LNA) with active bias and high isolation for use in cellular infrastructure applications. It is designed for a range of low noise, high linearity applications such as small cell, tower mounted amplifiers (TMA) and receiver front-end circuits. It operates from a single voltage supply and is suitable for applications with frequencies from 700 to 1400 MHz such as ISM, GSM, W-CDMA and LTE.

#### **Features**

- Ultra Low Noise Figure: 0.36 dB @ 900 MHz

- Frequency: 700-1400 MHz

- Unconditionally Stable Over Temperature

- High Reverse Isolation: -21 dB @ 900 MHz

- P1dB: 24.5 dBm @ 900 MHz

- Small-Signal Gain: 17.2 dB @ 900 MHz (adjustable externally)

- · Third Order Output Intercept Point: 37.4 dBm @ 900 MHz

- · Single 5 V Supply

- · Power-down Pin

- Supply Current: 55 mA

- 50 Ohm Operation (some external matching required)

- · Cost-effective 8-pin, 2 mm DFN Surface Mount Plastic Package

- In Tape and Reel. T1 Suffix = 1,000 Units, 12 mm Tape Width, 7-inch Reel.

#### Table 1. Typical Performance (1)

| Characteristic                        | Symbol         | 700<br>MHz      | 900<br>MHz | 1400<br>MHz     | Unit |

|---------------------------------------|----------------|-----------------|------------|-----------------|------|

| Noise Figure (2a)                     | NF             | 0.46 <b>(b)</b> | 0.36(b)    | 0.45 <b>(b)</b> | dB   |

| Input Return Loss<br>(S11)            | IRL            | -17             | -15        | -14             | dB   |

| Output Return Loss<br>(S22)           | ORL            | -14             | -15        | -15             | dB   |

| Small-Signal Gain<br>(S21)            | G <sub>p</sub> | 19              | 17.2       | 13.2            | dB   |

| Power Output @ 1dB Compression        | P1dB           | 24              | 24.5       | 24              | dBm  |

| Third Order Input<br>Intercept Point  | IIP3           | 17              | 20.2       | 23.8            | dBm  |

| Third Order Output<br>Intercept Point | OIP3           | 36              | 37.4       | 37              | dBm  |

# 1. $V_{DD} = 5$ Vdc, $T_A = 25$ °C, 50 ohm system, application circuit tuned for specified frequency.

# MML09231HT1

700-1400 MHz, 17.2 dB 24.5 dBm, 0.36 dB NF E-pHEMT LNA

DFN 2 ×

#### **Table 2. Maximum Ratings**

| Rating                    | Symbol           | Value       | Unit |

|---------------------------|------------------|-------------|------|

| Supply Voltage            | $V_{DD}$         | 6           | V    |

| Supply Current            | I <sub>DD</sub>  | 150         | mA   |

| RF Input Power            | P <sub>in</sub>  | 20          | dBm  |

| Storage Temperature Range | T <sub>stg</sub> | -65 to +150 | °C   |

| Junction Temperature      | T <sub>J</sub>   | 175         | °C   |

#### **Table 3. Thermal Characteristics**

| Characteristic                                                                             | Symbol         | Value <sup>(3)</sup> | Unit |

|--------------------------------------------------------------------------------------------|----------------|----------------------|------|

| Thermal Resistance, Junction to Case<br>Case Temperature 95°C, 5 Vdc, 55 mA, no RF applied | $R_{	heta JC}$ | 77                   | °C/W |

Refer to AN1955, Thermal Measurement Methodology of RF Power Amplifiers. Go to <a href="http://www.freescale.com/rf">http://www.freescale.com/rf</a>.

Select Documentation/Application Notes - AN1955.

<sup>2. (</sup>a) Noise figure value calculated with connector losses removed. (b)  $Z_{\text{in}}$  = 50  $\Omega.$

$\textbf{Table 4. Electrical Characteristics} \ (V_{DD} = 5 \ \text{Vdc}, \ 900 \ \text{MHz}, \ T_{A} = 25^{\circ}\text{C}, \ 50 \ \text{ohm system, in Freescale Application Circuit})$

| Characteristic                                                                   | Symbol          | Min      | Тур    | Max                    | Unit |

|----------------------------------------------------------------------------------|-----------------|----------|--------|------------------------|------|

| Small-Signal Gain (S21)                                                          | Gp              | 15.8     | 17.2   | _                      | dB   |

| Input Return Loss (S11)                                                          | IRL             | _        | -15    | _                      | dB   |

| Output Return Loss (S22)                                                         | ORL             | _        | -15    | _                      | dB   |

| Power Output @ 1dB Compression                                                   | P1dB            | _        | 24.5   | _                      | dBm  |

| Third Order Input Intercept Point                                                | IIP3            | _        | 20.2   | _                      | dBm  |

| Third Order Output Intercept Point                                               | OIP3            | _        | 37.4   | _                      | dBm  |

| Reverse Isolation (S12)                                                          | S12             | _        | -21    | _                      | dB   |

| Noise Figure (1)                                                                 | NF              | =        | 0.36   | =                      | dB   |

| Supply Current (2)                                                               | I <sub>DD</sub> | 40       | 55     | 70                     | mA   |

| Supply Voltage                                                                   | $V_{DD}$        | =        | 5      | =                      | V    |

| Supply Current in Power Down Mode                                                | I <sub>PD</sub> | =        | 1.1    | =                      | mA   |

| Logic Voltage for Power Down <sup>(3)</sup> Input High Voltage Input Low Voltage | V <sub>PD</sub> | 2.2<br>0 | _<br>_ | V <sub>DD</sub><br>0.5 | V    |

- 1. Noise figure value calculated with connector losses removed.

- 2. DC current measured with no RF signal applied.

- 3. Limits derived from device characterization.

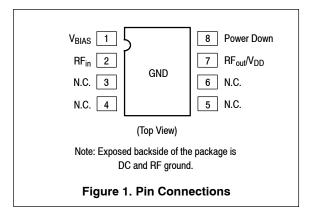

**Table 5. Functional Pin Description**

| Pin<br>Number | Pin Function                      |

|---------------|-----------------------------------|

| 1             | V <sub>BIAS</sub>                 |

| 2             | RF <sub>in</sub>                  |

| 3             | No Connection                     |

| 4             | No Connection                     |

| 5             | No Connection                     |

| 6             | No Connection                     |

| 7             | RF <sub>out</sub> /Supply Voltage |

| 8             | Power Down (active high)          |

#### **Table 6. ESD Protection Characteristics**

| Test Methodology                       | Class            |

|----------------------------------------|------------------|

| Human Body Model (per JESD 22-A114)    | 1B, passes 700 V |

| Machine Model (per EIA/JESD 22-A115)   | A                |

| Charge Device Model (per JESD 22-C101) | IV               |

# Table 7. Moisture Sensitivity Level

| Test Methodology                     | Rating | Package Peak Temperature | Unit |

|--------------------------------------|--------|--------------------------|------|

| Per JESD22-A113, IPC/JEDEC J-STD-020 | 1      | 260                      | °C   |

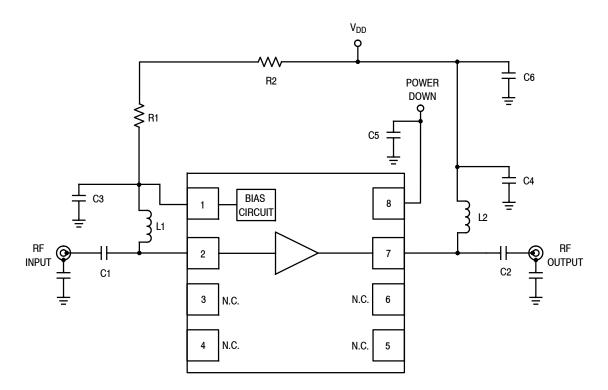

### **50 OHM APPLICATION CIRCUIT: 900 MHz**

Figure 2. MML09231H Test Circuit Schematic

Table 8. MML09231H Test Circuit Component Designations and Values

| Part   | Description                        | Part Number        | Manufacturer |

|--------|------------------------------------|--------------------|--------------|

| C1     | 100 pF Chip Capacitor              | GRM1555C1H101JA01  | Murata       |

| C2     | 180 pF Chip Capacitor              | GRM1555C1H181JA01  | Murata       |

| C3     | 27 pF Chip Capacitor               | GRM1555C1H270JA01  | Murata       |

| C4     | 220 pF Chip Capacitor              | GRM1555C1H221JA01  | Murata       |

| C5, C6 | 1000 pF Chip Capacitors            | GRM1885C1H102JA01  | Murata       |

| L1     | 20 nH Chip Inductor                | 0402HP-20NXGLW     | Coilcraft    |

| L2     | 47 nH Chip Inductor                | 0402HP-47NXGLW     | Coilcraft    |

| R1     | 4.7 kΩ, 1/10 W Chip Resistor       | CR21-472J-B        | Kyocera      |

| R2     | 0 Ω, 1 A Chip Resistor             | CR0402-J/-000GLFCT | Bourns       |

| PCB    | $0.02'',  \epsilon_{\rm f} = 3.50$ | RO4350B            | Rogers       |

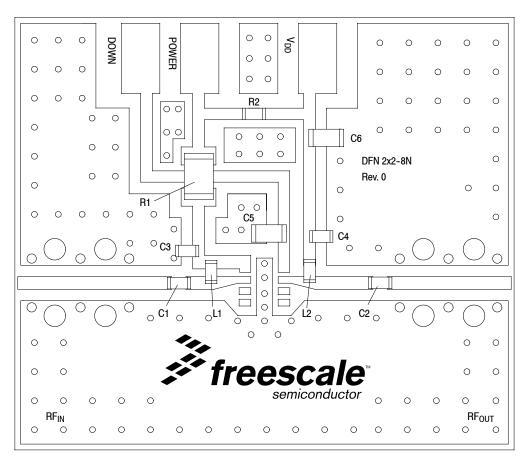

#### **50 OHM APPLICATION CIRCUIT: 900 MHz**

NOTE: To achieve optimal noise performance, it is critical that proper biasing, input matching, supply decoupling and grounding are employed.

Figure 3. MML09231H Test Circuit Component Layout

Table 8. MML09231H Test Circuit Component Designations and Values

| Part   | Description                    | Part Number        | Manufacturer |

|--------|--------------------------------|--------------------|--------------|

| C1     | 100 pF Chip Capacitor          | GRM1555C1H101JA01  | Murata       |

| C2     | 180 pF Chip Capacitor          | GRM1555C1H181JA01  | Murata       |

| C3     | 27 pF Chip Capacitor           | GRM1555C1H270JA01  | Murata       |

| C4     | 220 pF Chip Capacitor          | GRM1555C1H221JA01  | Murata       |

| C5, C6 | 1000 pF Chip Capacitors        | GRM1885C1H102JA01  | Murata       |

| L1     | 20 nH Chip Inductor            | 0402HP-20NXGLW     | Coilcraft    |

| L2     | 47 nH Chip Inductor            | 0402HP-47NXGLW     | Coilcraft    |

| R1     | 4.7 kΩ, 1/10 W Chip Resistor   | CR21-472J-B        | Kyocera      |

| R2     | 0 Ω, 1 A Chip Resistor         | CR0402-J/-000GLFCT | Bourns       |

| PCB    | $0.02''$ , $\epsilon_r = 3.50$ | RO4350B            | Rogers       |

(Test Circuit Component Designations and Values repeated for reference.)

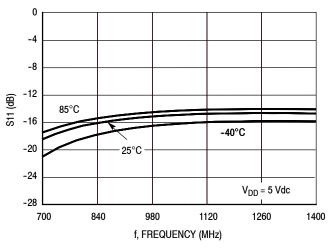

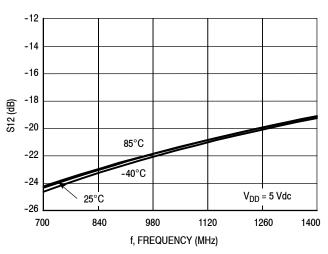

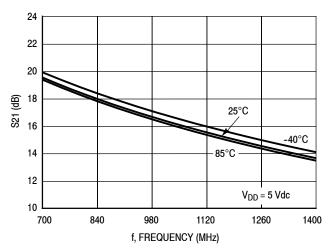

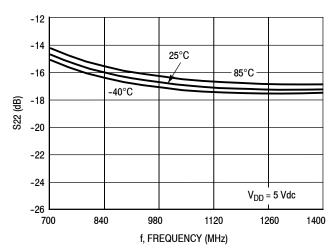

#### 50 OHM TYPICAL CHARACTERISTICS: 900 MHz

Figure 4. S11 versus Frequency versus Temperature

Figure 5. S12 versus Frequency versus Temperature

Figure 6. S21 versus Frequency versus Temperature

Figure 7. S22 versus Frequency versus Temperature

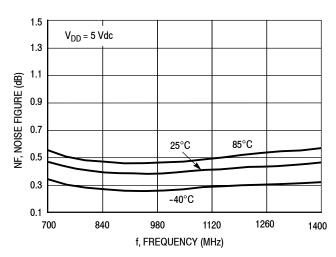

#### **50 OHM TYPICAL CHARACTERISTICS: 900 MHz**

Figure 8. Noise Figure versus Frequency versus Temperature

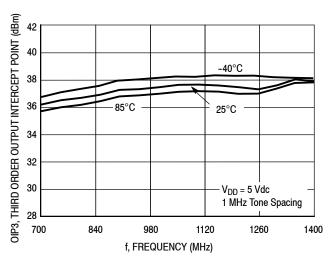

Figure 9. Third Order Output Intercept Point (Two-Tone) versus Frequency versus Temperature

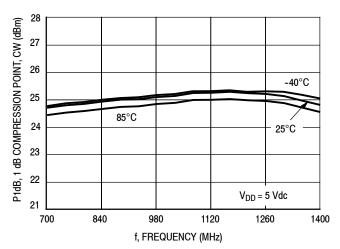

Figure 10. P1dB versus Frequency versus Temperature, CW

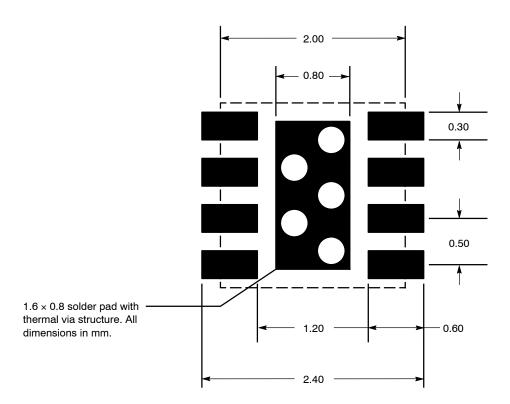

Figure 11. PCB Pad Layout for DFN 2  $\times$  2

Figure 12. Product Marking

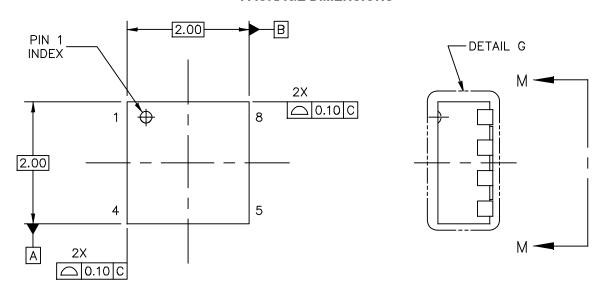

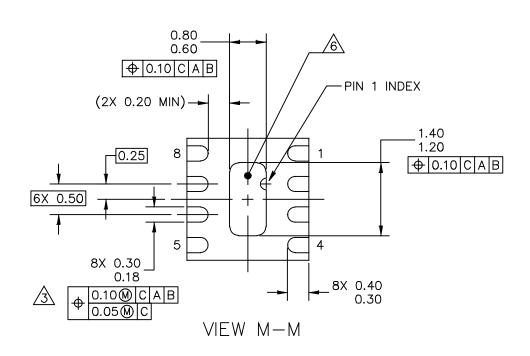

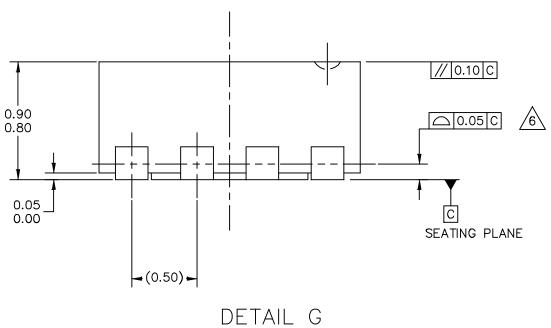

#### **PACKAGE DIMENSIONS**

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.         | MECHANICAL OUTLINE |                                 | PRINT VERSION NO | T TO SCALE |

|--------------------------------------------------------------|--------------------|---------------------------------|------------------|------------|

| TITLE: THERMALLY ENHANCED DUAL FLAT NON-LEADED PACKAGE (DFN) |                    | DOCUMENT NO: 98ASA00228D REV: 0 |                  | REV: 0     |

|                                                              |                    | CASE NUMBER: 2132-01 14 MAY 201 |                  |            |

| 8 TERMINAL, 0.5 PITCH (2 X                                   | 2 X 0.85)          | STANDARD: NON-JEDEC             |                  |            |

| $\Box$ | ET   | AIL  | _  | G  |    |

|--------|------|------|----|----|----|

| VIEW   | ROT. | ATED | 9( | Э. | CW |

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.      | MECHANICAL OUTLINE |                                  | PRINT VERSION NO | T TO SCALE |

|--------------------------------------------------------------|--------------------|----------------------------------|------------------|------------|

| TITLE: THERMALLY ENHANCED DUAL FLAT NON-LEADED PACKAGE (DFN) |                    | DOCUMENT NO                      | ): 98ASA00228D   | REV: 0     |

|                                                              |                    | CASE NUMBER: 2132-01 14 MAY 2010 |                  |            |

| 8 TERMINAL, 0.5 PITCH (2 X                                   | 2 X 0.85)          | STANDARD: NON-JEDEC              |                  |            |

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5 2009

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

- THIS DIMENSION APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15

AND 0.30mm FROM TERMINAL TIP. IF THE TERMINAL HAS THE OPTIONAL RADIUS ON THE

OTHER END OF THE TERMINAL, THIS DIMENSION SHOULD NOT BE MEASURED IN THAT

RADIUS AREA.

- 4. MAX. PACKAGE WARPAGE IS 0.05 mm.

- 5. MAXIMUM ALLOWABLE BURRS IS 0.076 mm IN ALL DIRECTIONS.

- 6. BILATERAL COPLANARITY ZONE APPLIES TO THE EXPOSED HEAT SINK SLUGAS WELL AS THE TERMINALS.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                                           | MECHANICAL OUTLINE |                          | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------------------------------------------------|--------------------|--------------------------|----------------------------|-------------|

| TITLE: THERMALLY ENHANCED DUAL FLAT NON-LEADED PACKAGE (DFN) 8 TERMINAL, 0.5 PITCH (2 X 2 X 0.85) |                    | DOCUMENT NO: 98ASA00228D |                            | REV: 0      |

|                                                                                                   |                    | CASE NUMBER              | 2: 2132–01                 | 14 MAY 2010 |

|                                                                                                   |                    | STANDARD: NON-JEDEC      |                            |             |

#### PRODUCT DOCUMENTATION, SOFTWARE AND TOOLS

Refer to the following resources to aid your design process.

#### **Application Notes**

AN1955: Thermal Measurement Methodology of RF Power Amplifiers

#### Software

.s2p File

#### **Development Tools**

· Printed Circuit Boards

For Software and Tools, do a Part Number search at http://www.freescale.com, and select the "Part Number" link. Go to Software & Tools on the part's Product Summary page to download the respective tool.

#### **FAILURE ANALYSIS**

At this time, because of the physical characteristics of the part, failure analysis is limited to electrical signature analysis. In cases where Freescale is contractually obligated to perform failure analysis (FA) services, full FA may be performed by third party vendors with moderate success. For updates contact your local Freescale Sales Office.

#### **REVISION HISTORY**

The following table summarizes revisions to this document.

| Revision | Date       | Description                                                                                                                   |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------|

| 0        | May 2013   | Initial Release of Data Sheet                                                                                                 |

| 1        | Sept. 2014 | Table 2, Maximum Ratings: updated Junction Temperature from 150°C to 175°C to reflect recent test results of the device, p. 1 |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners.

© 2013-2014 Freescale Semiconductor, Inc.

Document Number: MML09231H

Rev. 1, 9/2014