# 256M-BIT 3.0-VOLT PARALLEL FLASH MEMORY WITH PAGE MODE

| 1                |                                  | General Description     |                                        |    |  |  |

|------------------|----------------------------------|-------------------------|----------------------------------------|----|--|--|

| 2                |                                  | FEAT                    | JRES                                   | 8  |  |  |

| 3                |                                  | PIN C                   | ONFIGURATION                           | 9  |  |  |

| 4                | BLOCK DIAGRAM                    |                         |                                        |    |  |  |

| 5                |                                  | PIN D                   | ESCRIPTION                             | 11 |  |  |

| 6                |                                  | Introd                  | uction                                 | 12 |  |  |

| 7                |                                  | ARRA                    | Y ARCHITECTURE                         | 15 |  |  |

|                  | 7.1                              | Flas                    | sh Main Memory Array                   | 17 |  |  |

|                  | 7.2                              | CFI                     | and Device ID (CFI-ID)                 | 17 |  |  |

|                  | 7.3                              | Stat                    | us Register                            | 18 |  |  |

|                  | 7.4                              | Dat                     | a Polling Status                       | 19 |  |  |

|                  | 7.5                              | Sec                     | tor Protection Control                 | 19 |  |  |

|                  |                                  | 7.5.1                   | Lock Register                          | 19 |  |  |

|                  |                                  | 7.5.2                   | Individual Protection Bits (IPB)       | 19 |  |  |

|                  |                                  | 7.5.3                   | IPB Lock                               | 20 |  |  |

|                  |                                  | 7.5.4                   | Dynamic Protection Bits (DPB)          | 20 |  |  |

| 8                |                                  | Functi                  | onal Descriptions                      | 20 |  |  |

|                  | 8.1                              | Rea                     | ıd                                     | 20 |  |  |

|                  |                                  | 8.1.1                   | Random Read                            | 20 |  |  |

|                  |                                  | 8.1.2                   | Page Read                              | 21 |  |  |

|                  | 8.2                              | Dev                     | ice Reset Operations                   | 21 |  |  |

|                  | 8.3                              | Sta                     | ndby Mode                              | 22 |  |  |

|                  | 8.4                              | 8.4 Automatic Sleep     |                                        | 22 |  |  |

|                  | 8.5                              | 3.5 Output Disable Mode |                                        | 22 |  |  |

|                  | 8.6 Program Methods              |                         | gram Methods                           | 23 |  |  |

|                  |                                  | 8.6.1                   | Asynchronous Write                     | 23 |  |  |

|                  |                                  | 8.6.2                   | Word Programming                       | 23 |  |  |

|                  |                                  | 8.6.3                   | Write Buffer Programming               | 25 |  |  |

|                  | 8.7                              | Pro                     | gram Suspend / Program Resume Commands | 30 |  |  |

|                  | 8.8                              | Era                     | se Methods                             | 31 |  |  |

|                  |                                  | 8.8.1                   | Chip Erase                             | 31 |  |  |

|                  |                                  | 8.8.2                   | Sector Erase                           | 32 |  |  |

|                  | 8.9 Erase Suspend / Erase Resume |                         | se Suspend / Erase Resume              | 33 |  |  |

| 8.10 Blank Check |                                  |                         | nk Check                               | 34 |  |  |

## winbond ==== 8.11 Enhanced Sector Protection Methods..... 8.11.3 Individual Protection Bits (IPB).......37 8.13 Monitoring Device Status......40 8.13.2 Data Polling Status .......41 8.20 Common Flash Interface and Device ID (CFI-ID) .......57 Electrical Specifications 62 Absolute Maximum Ratings.......62 9.1.1 9.2.1 9.2.2 9.2.3 Power Up and Power-Down .......63 10.2 Power Up Reset and Hardware Reset ......69

| Δ  |           | s winbond                                                    |    |

|----|-----------|--------------------------------------------------------------|----|

|    | 10.2.1    | Power Up Reset                                               | 69 |

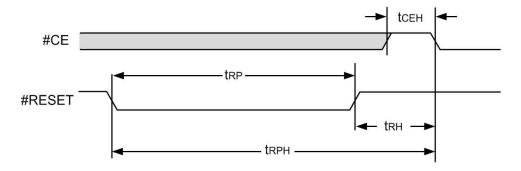

|    | 10.2.2    | Hardware Reset                                               | 71 |

| 1  | 0.3 AC C  | Characteristics                                              | 72 |

|    | 10.3.1    | Internal Algorithm Performance Table                         | 72 |

|    | 10.3.2    | Asynchronous Read Operations                                 | 73 |

|    | 10.3.3    | Asynchronous Write Operations                                | 75 |

|    | 10.3.4    | Alternate #CE Controlled Write Operations                    | 81 |

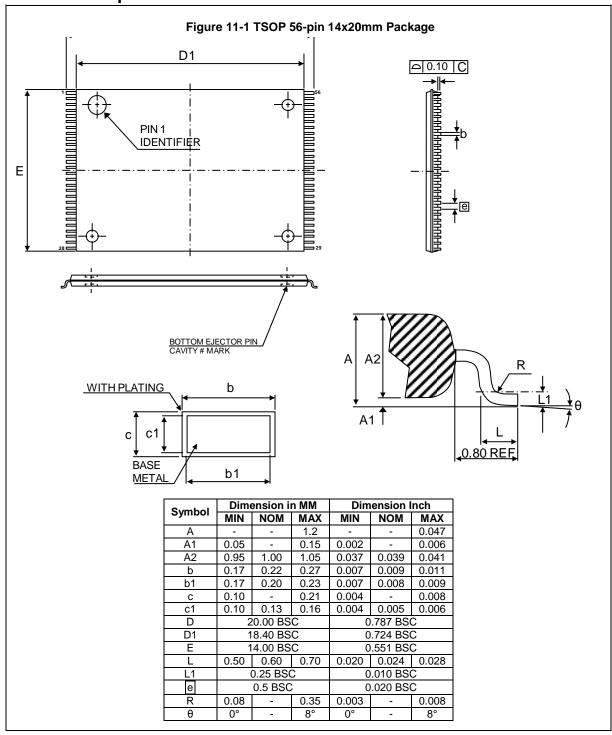

| 11 | Packag    | ge Dimensions                                                | 83 |

| 1  | 1.1 TSO   | P 56-pin 14x20mm                                             | 83 |

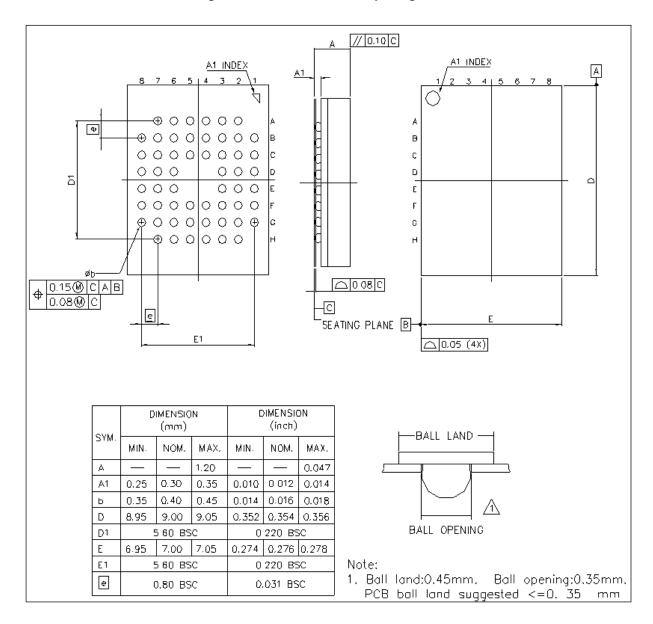

| 1  | 1.2 Thin  | & Fine-Pitch Ball Grid Array, 56 ball, 7x9mm (TFBGA56)       | 84 |

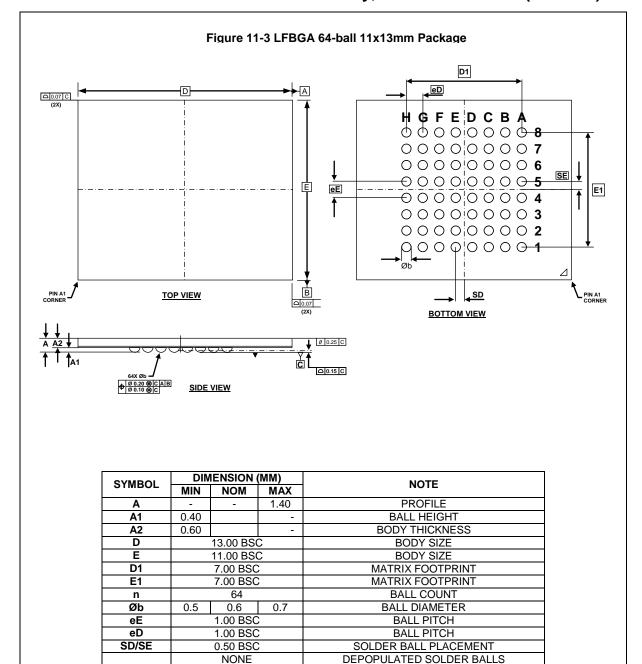

| 1  | 1.3 Low-  | Profile Fine-Pitch Ball Grid Array, 64-ball 11x13mm (LFBA64) | 85 |

| 12 | Orderin   | ng Information                                               | 86 |

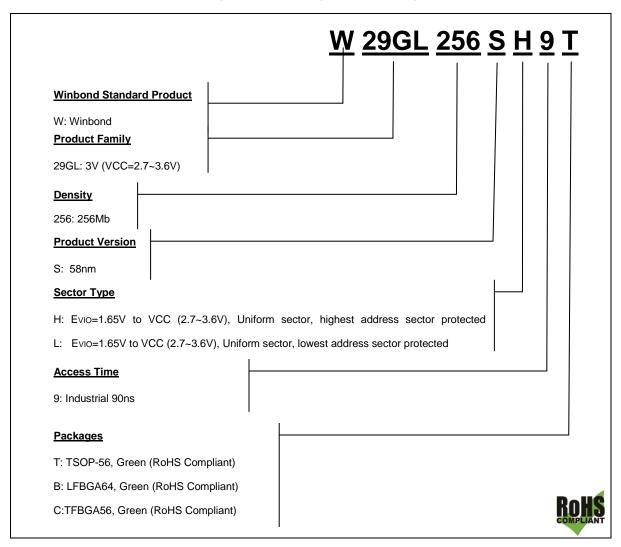

| 1  | 2.1 Orde  | ering Part Number Definitions                                | 86 |

| 1  | 2.2 Valid | Part Numbers and Top Side Marking                            | 87 |

| 13 | History   |                                                              | 88 |

|    |           |                                                              |    |

| Table 5-1 Pin Description                                                       | 11 |

|---------------------------------------------------------------------------------|----|

| Table 6-1 W29GL256S Address Map                                                 | 14 |

| Table 7-1 W29GL256S Sector and Memory Address Map                               | 17 |

| Table 7-2 CFI-ID Address Map Overview                                           | 18 |

| Table 8-1 Write Buffer Programming Command Sequence                             | 30 |

| Table 8-2 Sector Protection Status                                              | 38 |

| Table 8-3 Lock Register                                                         | 38 |

| Table 8-4 Security Sector Region                                                | 39 |

| Table 8-5 Status Register                                                       | 40 |

| Table 8-6 Data Polling Status                                                   | 47 |

| Table 8-7 Interface Conditions                                                  | 50 |

| Table 8-8 Read, Write, Program and Erase Definitions                            | 51 |

| Table 8-9 CFI-ID (Autoselect) Definitions                                       | 52 |

| Table 8-10 Security Sector Region Command Definitions                           | 52 |

| Table 8-11 Lock Register Command Set Definitions                                | 53 |

| Table 8-12 IPB Non-Volatile Sector Protection Command Set Definitions           | 53 |

| Table 8-13 Global Non-Volatile Sector Protection Freeze Command Set Definitions | 54 |

| Table 8-14 DPB Volatile Sector Protection Command Set Definitions               | 54 |

| Table 8-15 ID (Autoselect) Address Map                                          | 57 |

| Table 8-16 CFI Query Identification String                                      | 59 |

| Table 8-17 CFI System Interface String                                          | 59 |

| Table 8-18 CFI Device Geometry Definition                                       | 60 |

| Table 8-19 CFI Primary Vendor-Specific Extended Query                           | 61 |

| Table 9-1 Absolute Maximum Ratings                                              | 62 |

| Table 9-2 Power Up/Power-Down Voltage and Timing                                | 63 |

| Table 9-3 DC Characteristics                                                    | 65 |

| Table 9-4 Connector Capacitance for FBGA (LFBGA64) Package                      | 67 |

| Table 9-5 Connector Capacitance for TSOP (TSOP56) Package                       | 67 |

| Table 9-6 Connector Capacitance for TFBGA (TFBGA56) Package                     | 67 |

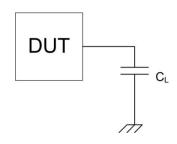

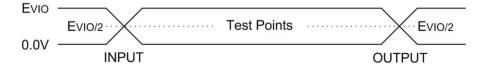

| Table 10-1 Test Specification                                                   | 68 |

| Table 10-2 Power ON and Reset Parameters                                        | 69 |

| Table 10-3 Internal Algorithm Characteristics                                   | 72 |

| Table 10-4 Read Operation EVIO = 1.65V to VCC, VCC = 2.7V to 3.6V               | 73 |

| Table 10-5 Write Operations                                                     | 75 |

| <b>FERRISH WINDONG</b>                                                 |                   |

|------------------------------------------------------------------------|-------------------|

| Table 10-6 Erase/Program Operations                                    | 78                |

| Table 10-7 Alternate #CE Controlled Write Operations                   | 81                |

| Table 12-1 Valid Part Numbers and Markings                             | 87                |

| Table 13-1 Revision History                                            | 88                |

| TABLE OF FIGURES                                                       |                   |

| Figure 3-1 LFBGA64 TOP VIEW (Face Down)                                | 9                 |

| Figure 3-2 56-PIN STANDARD TSOP (Top View)                             | 9                 |

| Figure 3-3 TFBGA56 TOP VIEW (Face Down)                                | 9                 |

| Figure 4-1 Simplified Block Diagram                                    | 10                |

| Figure 8-1 Word Program Operation                                      | 25                |

| Figure 8-2 Write Buffer Programming Operation with Data Polling Status | 28                |

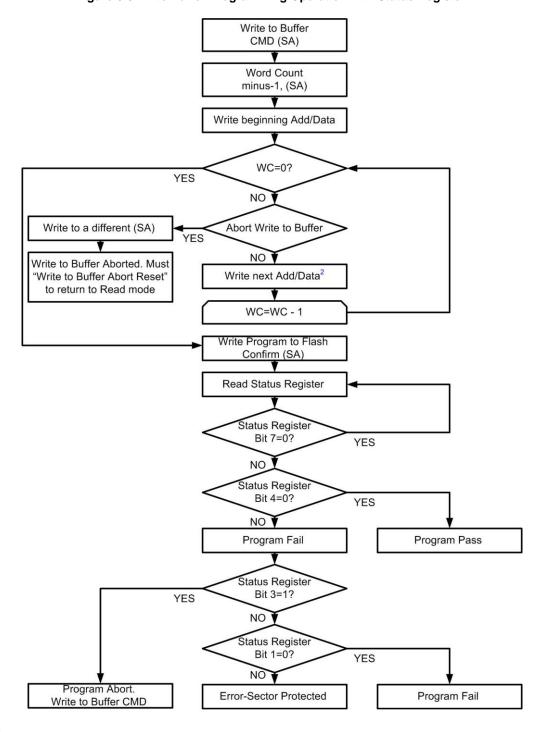

| Figure 8-3 Write Buffer Programming Operation with Status Register     | 29                |

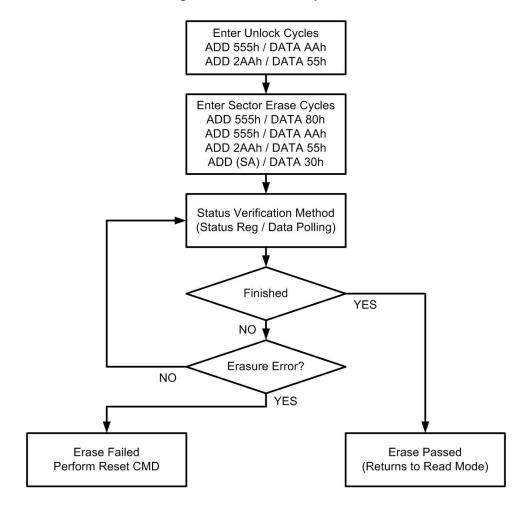

| Figure 8-4 Sector Erase operation                                      | 33                |

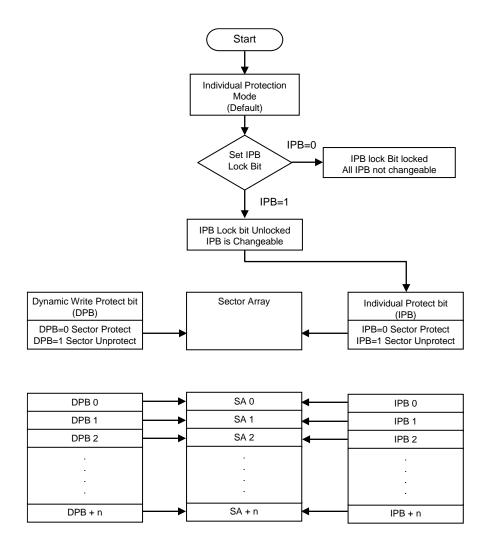

| Figure 8-5 Enhanced Sector Protection IPB Program Algorithm            | 36                |

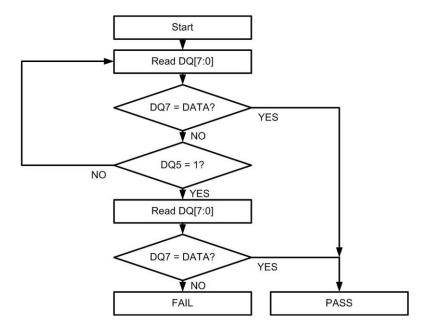

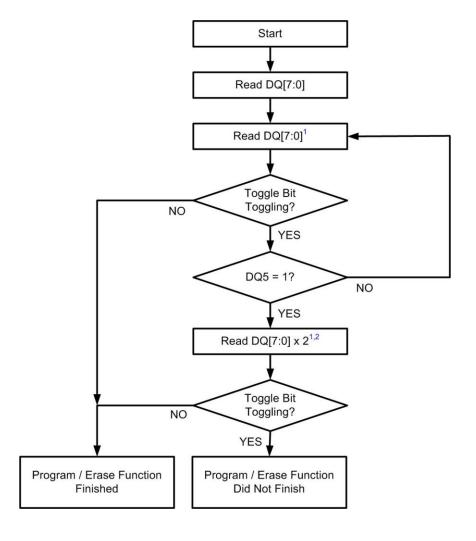

| Figure 8-6 Data# Polling Algorithm                                     | 42                |

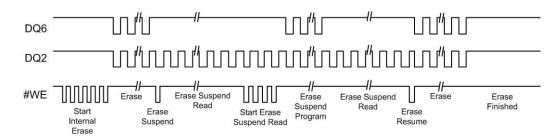

| Figure 8-7 Toggle Bit Program                                          | 46                |

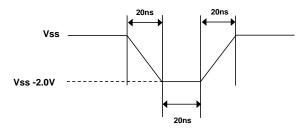

| Figure 9-1 Max Negative Overshoot Waveform                             | 62                |

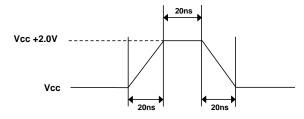

| Figure 9-2 Positive Overshoot Waveform                                 | 62                |

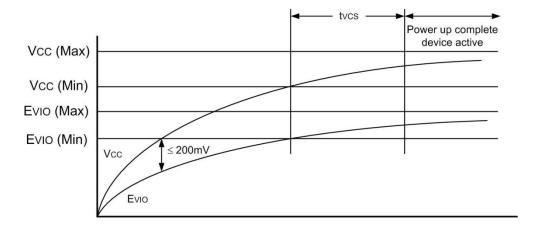

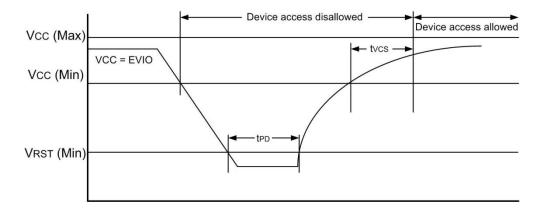

| Figure 9-3 Power-up                                                    | 64                |

| Figure 9-4 Power-down and Voltage Drop                                 | 64                |

| Figure 10-1 Device Under Test Setup                                    | 68                |

| Figure 10-2 Input Switching Test Waveforms                             | 68                |

| Figure 10-3 Power Up Reset                                             | 70                |

| Figure 10-4 Hardware Reset                                             | 71                |

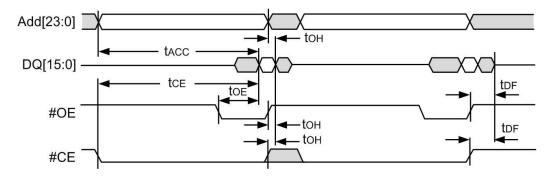

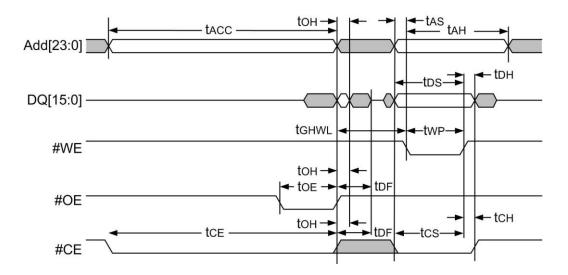

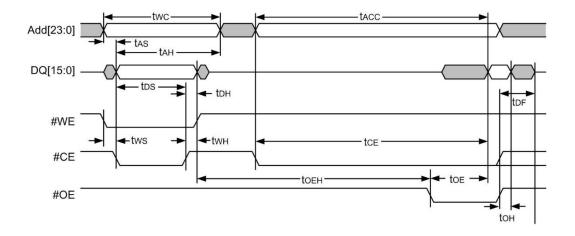

| Figure 10-5 Back to Back Read (tACC) Operation                         | 73                |

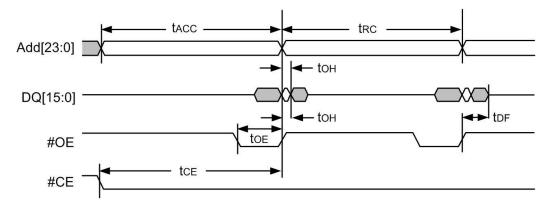

| Figure 10-6 Back to Back Read Operation (tRC)                          | 74                |

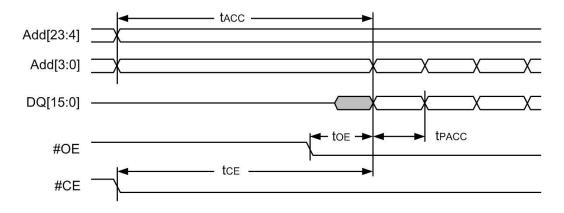

| Figure 10-7 Page Read                                                  | 74                |

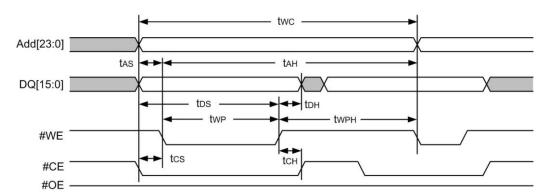

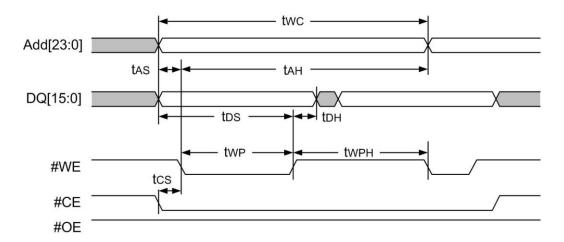

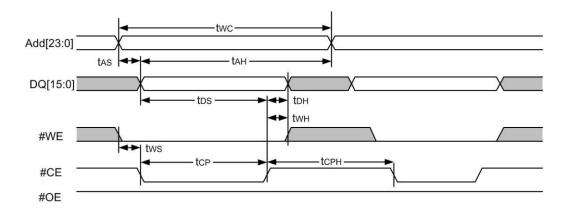

| Figure 10-8 Back to Back Write Operation                               | 75                |

| Figure 10-9 Back to Back (#CE VIL) Write Operation                     | 76                |

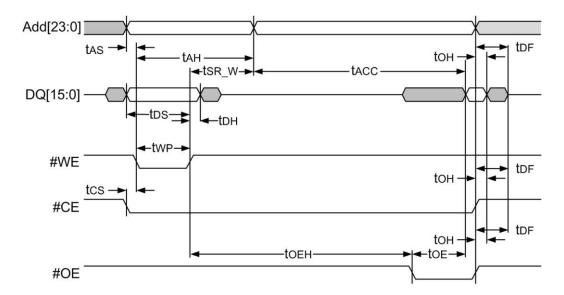

| Figure 10-10 Write to Read (tACC) Operation                            | 76                |

| Figure 10-11 Write to Read (tCE) Operation                             | 77                |

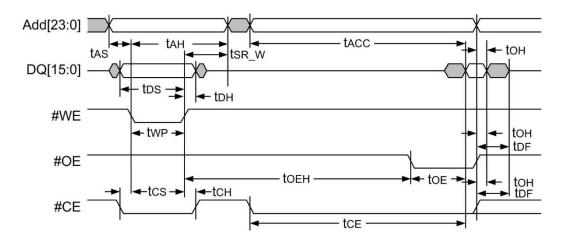

| Figure 10-12 Read to Write (#CE VIL) Operation                         | 77                |

| Figure 10-13 Read to Write (#CE Toggle) Operation                      |                   |

| Dublication Palaces                                                    | Data: 1.1.00 0044 |

| <b>F</b> FFF WINDONG FFF                                |    |

|---------------------------------------------------------|----|

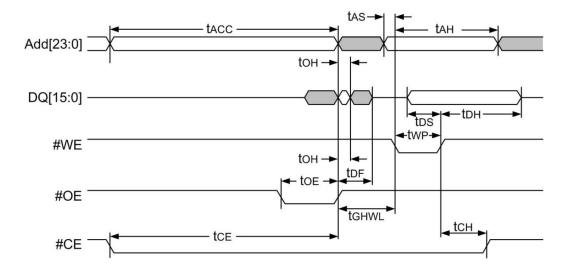

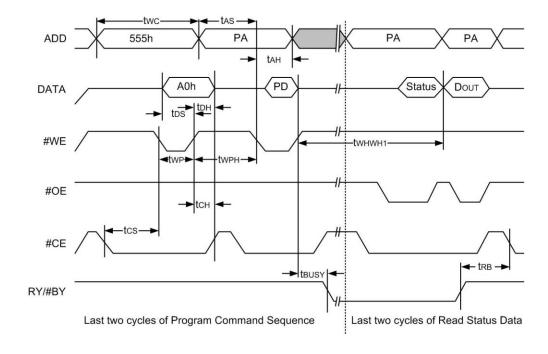

| Figure 10-14 Program Operation                          |    |

| Figure 10-15 Chip/Sector Erase Operation                | 79 |

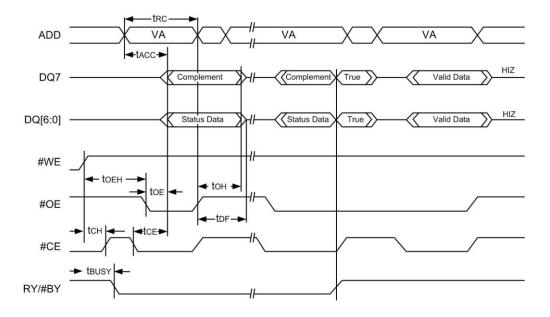

| Figure 10-16 Data# Polling (During Internal Algorithms) | 80 |

| Figure 10-17 Toggle Bit (During Internal Algorithms)    | 80 |

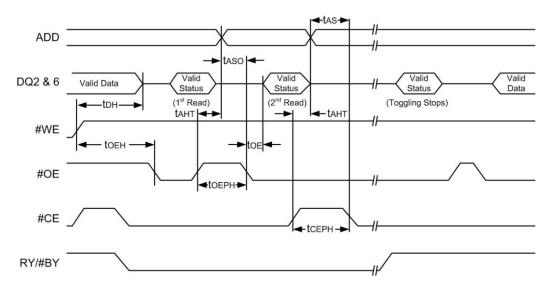

| Figure 10-18 DQ2 vs. DQ6 Comparison Timing              | 81 |

| Figure 10-19 Back to Back (#CE) Write Operation         | 82 |

| Figure 10-20 (#CE) Write to Read Operation              | 82 |

| Figure 11-1 TSOP 56-pin 14x20mm Package                 | 83 |

| Figure 11-2 TFBGA-56, 7x9mm package                     | 84 |

| Figure 11-3 LFBGA 64-ball 11x13mm Package               | 85 |

| Figure 12-1 Ordering Part Numbering                     | 86 |

#### 1 GENERAL DESCRIPTION

The W29GL256S Parallel Flash memory provides a storage solution for embedded system applications that require better performance, lower power consumption and higher density. This product fabricated on 58 nm process technology. This device offers a fast page access time as fast as 15ns with a corresponding random access time as fast as 90ns. It features a Write Buffer that allows a maximum of 256 words (512 bytes) to be programmed in one operation, resulting in faster effective programming time than standard programming algorithms. The W29GL256S also offers special features such as Compatible Manufacturer ID that makes the device industry standard compatible without the need to change firmware.

#### 2 FEATURES

- 58 nm Technology

- x16 data bus

- 256-WORD (512-byte) Programming Buffer

- Programming in Page multiples, up to a maximum of 512 bytes

- Asynchronous 32-byte Page Read

- Single word and multiple program on same word options

- Sector Erase

Uniform 128-kbyte sectors

- Enhanced Sector Protection (ESP)

- Volatile and non-volatile protection methods for each sector

- Security Sector Region

- 1024-byte One Time Program (OTP) array divided into two 512-Byte lockable regions

- Suspend and Resume commands for Program and Erase operations

- Status Register, Data Polling, and Ready/Busy pin methods to determine device status

- CFI (Common Flash Interface) support

- Single supply (VCC) for read / program / erase (2.7V to 3.6V)

- Enhanced Variable I/O Feature

Enhanced I/O voltage range (EVIO):

1.65V to VCC

- Wide Temperature Range (-40°C to +85°C)

- More than 100,000 erase/program cycles

- 20-year data retention typical

- · Packaging Options

- o 56-pin TSOP, 14x20mm

- o 56-ball TFBGA, 7x9mm

- o 64-ball LFBGA, 13x11 mm

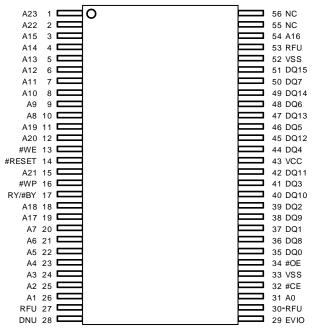

#### 3 PIN CONFIGURATION

Figure 3-1 LFBGA64 TOP VIEW (Face Down)

F8 NC A8 NC C8 A23 E8 VSS (E7) A16 (E6) D07 (E5) D05 (E4) D02 (E2) A2 (E1) G8 NC A22 EVIO NC (G) DQ 15 (G) DQ 15 (G) DQ 10 (G) DQ (G) #(G) H7 VSS C7 A14 C6 A10 C5 A21 A18 C3 A6 C2 A2 D7 A15 D6 A11 D5 A19 A20 D3 A5 D2 A1 F7 RFU F6 DQ14 F5 DQ12 F4 DQ10 F3 DQ8 F2 #CE B6 A8 B5 #RESET (H6) DQ6 H5 DQ4 H4 DQ3 #WP B3 A17 (H3) DQ1 (H2) VSS (F1) (H1)

Figure 3-2 56-PIN STANDARD TSOP (Top View)

Figure 3-3 TFBGA56 TOP VIEW (Face Down)

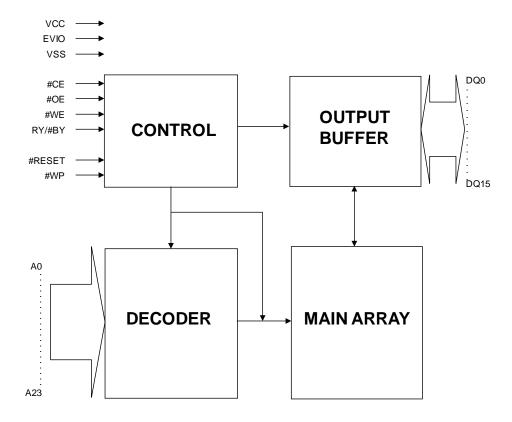

### **4 BLOCK DIAGRAM**

Figure 4-1 Simplified Block Diagram

## **5 PIN DESCRIPTION**

#### **Table 5-1 Pin Description**

| SYMBOL   | SIGNAL<br>TYPE | PIN NAME                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A0-A23   | Input          | Address Inputs                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| DQ0-DQ15 | I/O            | Data Inputs/Outputs                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| #CE      | Input          | Chip Enable, Device selected at VIL                                                                                                                                                                                                                                                                                                                                                                                     |  |

| #OE      | Input          | Output Enable, Output at VIL and HIGH-Z at VIH                                                                                                                                                                                                                                                                                                                                                                          |  |

| #WE      | Input          | Write Enable, Write Mode at VIL and Read Mode at VIH                                                                                                                                                                                                                                                                                                                                                                    |  |

| #WP      | Input          | Hardware Write Protect, Highest & Lowest Sector Protect at VIL                                                                                                                                                                                                                                                                                                                                                          |  |

| #RESET   | Input          | Hardware Reset, device logic to standby and ready to read.                                                                                                                                                                                                                                                                                                                                                              |  |

| RY/#BY   | Output         | Ready/Busy Status, Indicates whether an Embedded Algorithm is in progress or complete. At VIL, the device is actively engaged in an Embedded Algorithm such as erasing or programming. At HIGH-Z, the device is ready for read or a new command write requires external pull-up resistor to detect the HIGH-Z state. Multiple devices may have their RY/#BY outputs tied together to detect when all devices are ready. |  |

| VCC      | Power Supply   | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Evio     | Power Supply   | Enhanced Variable IO Supply                                                                                                                                                                                                                                                                                                                                                                                             |  |

| VSS      | Power Supply   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| NC       | -              | No Connection                                                                                                                                                                                                                                                                                                                                                                                                           |  |

#### 6 INTRODUCTION

The W29GL256S is a 3V, 256-Mbit, non-volatile, flash memory device with variable I/O. The device has a bus width of 16-bits (2-Bytes/1-Word) and word address boundaries are what are used. All read accesses provide 16 bits of data on every bus cycle. Every write cycle transfers 16 bits of data on the bus.

XIP and Data Storage flash memories are combined features of the W29GL256S. This enables the ability of fast programming speeds and reduced random access time of XIP flash in higher densities.

Read access to any random location takes 90 ns to 100 ns depending on device I/O power supply voltage. Each random access reads an aligned group of data of 32-bytes called a Page. Other words within the same Page may be read by changing only the low order 4 bits of word address. While in the same Page, access could take between 15 ns to 30 ns. This read operation is referred as Page Mode. Higher word address bits will select a different Page and begin another initial access. All read accesses are asynchronous.

The device control logic is divided into two parallel operating subsections, the Command State Machine (CSM) and the Write State Controller. Device level signals with the host system during read and write transfers are monitored by the CSM as needed for the inputs and drive outputs. CSM delivers data from the current entered address map on read operations; places write address and data information into the Write State Controller command memory; signals the Write State Controller of power level changes, write operations and hardware reset, The Write State Controller looks in the command memory, after a write operation, for correct command sequences and performs Internal Algorithms that are related.

Within the W29GL256S lie internal complex sequential operations or algorithms that are necessary to change the state of non-volatile data in the memory array. The internal Write State Controller manages all device algorithms. The main array data, programming and erasure are the main algorithms that are performed. When the host system sends command instructions to the flash device address space and Write State Controller receives these commands, provides status information during the progress of internal algorithms and performs all the necessary steps to complete the command.

A logical 1 bit is considered an erased cell. Changing a bit from a logical 1 to a logical 0 is considering programming. Note, only an erase operation is able to change a 0 to a 1. A restriction to an erase operation is a minimum of an entire sector (sector erase), which is a 128-kbyte aligned and length group of data is erased or the entire array can be erased (chip erase). Winbond ships the W29GL256S with all sectors erased.

The W29GL256S programming algorithm transfers volatile data from a write buffer to a non-volatile memory array line; this is called Write Buffer Programming. The size of the buffer is 256-Words (512-Bytes). 1 to 256 words can be written at any location in the Write Buffer prior to executing the programming operation. The programming operation can only be performed on an aligned group of 512 bytes in the flash array which is referred to as a Line.

After the completion of any Write Buffer operation or a reset, the buffer is refreshed to all 1's. By default any location that has not be written to a 0 are filled with 1's. Each page of data that was loaded into the Write Buffer during a programming operation, the memory array data is unaffected by 1's in the Write Buffer as it is transferred to a memory array Line.

Program and Erase operations may be affected by the Enhanced Sector Protection (ESP) methods, preventing any erasure or programming in a sector that may have been previously protected.

Table 6-1 W29GL256S Address Map

| Addresses Value                |      | Description                   |  |

|--------------------------------|------|-------------------------------|--|

| A3 - A0                        | 16   | Word Selection                |  |

| A7 - A0                        | 256  | Write Buffer Internal Address |  |

| A15 - A4                       | 4096 | Page Selection                |  |

| A15 - A8                       | 256  | Write-Buffer-Line Selection   |  |

| A23 - A16 256 Sector Selection |      | Sector Selection              |  |

#### 7 ARRAY ARCHITECTURE

There are several separate address spaces (i.e., Memory Map Overlay) that may appear within the address range of the flash memory device. Only one MMO can exist or be entered at a time.

- Main Memory Array

- This non-volatile area is used for storage of data that may be randomly accessed by asynchronous read operations.

- ID/CFI

- A Winbond factory programmed area for device characteristics information. It contains the Common Flash Interface (CFI) and Device Identification (ID) information tables.

- Security Sector Region (SSR)

- A Non-volatile / One Time Programmable (OTP) memory array used for Winbond factory and customer programmable permanent data.

- Lock Register

- This OTP non-volatile word is used to configure the Enhanced Sector Protection (ESP) features and lock the SSR.

- Individual Protection Bits (IPB):

- A non-volatile flash memory array with one bit for its associated sector. Programming this bit protects that sector from programming and erasure.

- IPB Lock

- Program and erase protection for the IPB bits. When the volatile register bit is enabled no programming or erasing of the IPB bits is prohibited.

- Dynamic Protection Bits (DPB)

- Similar to the IPB scheme, this volatile array with one bit for each sector can protect its associated sector from erasure and programming while the device is powered.

- Status Register

- Internal algorithm status monitoring can be done using this volatile register.

- Data Polling Status:

- Legacy software compatible volatile register used as an alternative to the Status Register to monitor internal algorithm status.

The Main Memory Array is the primary and default address space. This area at any time may be overlaid by one other address space. All the aforementioned address spaces are considered as a Memory Map Overlay (MMO). Each MMO replaces the entire address range of the main array. Addresses outside the current MMO address map are considered as not defined and are reserved for

future use. Read access is possible outside of an MMO address map and will return non-valid (undefined) data.

What appears in the flash device address space at any given time is one of four address map modes:

- Read Mode

- Memory Map Overlay (MMO) Mode

- Status Register (SR) Mode

- Data Polling Mode

In Read Mode the entire Flash Memory Array may be directly read. Read mode is entered during Power Up, after a Hardware Reset, Command Reset completion, or when an internal algorithm is suspended, all of which is controlled by the Write State Controller. While in the Read Mode, command accesses are permitted when an internal algorithm is suspended. There are subsets of commands that will be accepted in Read Mode while an Internal Algorithm is suspended.

The Status Register read command can be issued in any mode. This execution will cause the MMO of the Status Register to appear in the device address space at every word address location. To do this, the device interface waits for a read access, ignoring any write access. The content of the Status Register is presented at the next read access, after which it exits the Status Register MMO, and returns to the previous mode in which the Status Register read command was received.

While the Write State Controller is performing an internal algorithm, such as a non-volatile memory array program or an erase operation, none of the Main Memory Array is accessible because, the entire flash device address space is replaced by the MMO of the Data Polling Status at every word location in the device address space.

While in an internal algorithm operation, only the Status Register Read command or a Program / Erase suspend command will be accepted, ignoring all other commands. Hence, no other MMO may be entered.

The Data Polling MMO is visible during an internal algorithm operation and once a suspend command has been executed it is present up to the moment the device suspends the internal algorithm. When the internal algorithm is suspended the Data Polling MMO is exited and the Main Memory Array data is available again. The Data Polling MMO is activated again when the suspended internal algorithm operation is resumed. At the completion of an internal algorithm operation, the Data Polling MMO is exited and the device goes back to operation from which it was called.

As mentioned previously, only one MMO may exist at any one time. Device commands affect only the currently entered MMO. Not all commands are valid for each MMO. For a listed of valid commands, see the *Command Definition Tables* in MMO sections of the table.

Some MMOs have non-volatile data that can be programmed

- Individual Protection Bits (IPB), also erase capable

- Lock Register

- Security Sector Region

Operating in a non-volatile MMO mode while performing a program or erase command, the MMO is not readable while the internal algorithms is active. As soon as the function has completed, the MMO mode remains active and is again readable. Suspend and Resume commands are ignored for these non-volatile modes while these internal algorithms are active.

## 7.1 Flash Main Memory Array

The W29GL256S family is comprised of uniform 128KB sector size architecture. The table below shows the sector architecture of the W29GL256S device.

Table 7-1 W29GL256S Sector and Memory Address Map

| Sector | Sector Address<br>A23-A16 | Sector Size<br>(KByte) | Start    | X16<br>/ Finish |

|--------|---------------------------|------------------------|----------|-----------------|

| SA00   | 0000000                   | 128                    | 0000000h | 000FFFFh        |

| SA01   | 0000001                   | 128                    | 0010000h | 001FFFFh        |

|        | •                         |                        |          |                 |

|        | •                         |                        |          |                 |

|        | •                         | -                      |          |                 |

| SA254  | 11111110                  | 128                    | 0FE0000h | 0FEFFFFh        |

| SA255  | 11111111                  | 128                    | 0FF0000h | 0FFFFFFh        |

**Note:** This table has been reduced to show relative sector information for the entire device's individual sectors and their address ranges (sectors SA02-SA253 are not shown).

## 7.2 CFI and Device ID (CFI-ID)

There are two methods for systems to identify the type of flash memory installed in the system. The first method is called the Common Flash Interface (CFI). The second method called Autoselect, which is now referred to as Device Identification (ID).

Device Identification (ID), a command is used to enable a Memory Map Overlay where up to 16 word locations can be read to get JEDEC manufacturer identification (ID), device ID, and some configuration and protection status information from the flash memory.

17

The Common Flash Interface (CFI) command enables a Memory Map Overlay where a table of standard information about how the flash memory is organized and operates can be read.

Typically, these two address spaces have used separate commands and had separate overlays and are non-overlapping, so they actually can be combined in a single overlay. Either of these two commands can be used to access the combined Autoselect (ID) and CFI overlay.

The CFI-ID address map overlays the Flash Array data of the sector selected by the address used in the CFI-ID enter command. While the CFI-ID MMO is entered, the content of all other sectors is undefined. Address map starts at location 0 of the selected sector. Data is considered as undefined past the maximum defined address of the CFI-ID MMO to the maximum address of the selected sector.

To enter the Manufacturer ID (Autoselect) and Common Flash Interface (CFI) MMO command modes see the *Instruction Definition Table*.

**Table 7-2 CFI-ID Address Map Overview**

| Word Address          | Description                                  | Read / Write |

|-----------------------|----------------------------------------------|--------------|

| (SA) + 0000h to 000Fh | Device ID (traditional<br>Autoselect values) | Read Only    |

| (SA) + 0010h to 0079h | CFI data structure                           | Read Only    |

| (SA) + 0080h to FFFFh | Undefined                                    | Read Only    |

For the complete address map see the Device ID and Common Interface Tables.

## 7.3 Status Register

The Status Register, Memory Map Overlay (MMO) contains status for Internal Algorithms in a single volatile word format. When the read command for the Status Register is issued, status at the time of captured is presented in the register and the MMO is entered. All word locations in the device address space contain the Status Register information. Status Register exits the MMO mode after the first read access and returns to the address space map in use when the Status Register read command was issued.

## 7.4 Data Polling Status

The Data Polling Status, Memory Map Overlay (MMO) monitors the progress of Internal Algorithms which is contained in a single volatile word. Following the last write cycle of any command sequence that initiates an Internal Algorithms, the Data Polling Status will be entered. Internal Algorithms are initiated by one of the following commands:

- Blank Check

- Chip Erase

- Sector Erase

- Erase Resume / Program Resume

- Word Program

- Program Buffer to Flash

- Program Resume Enhanced Method

- Lock Register Program

- IPB Program

- All IPB Erase

At all word locations in the device address space, the Data Polling Status word appears. Data Polling Status MMO is exited and the device address space returns to the address map mode where the Internal Algorithms was started at the completion of the Internal Algorithms.

#### 7.5 Sector Protection Control

#### 7.5.1 Lock Register

The Lock Register, Memory Map Overlay (MMO) mode contains a single word of One Time Programmable (OTP) memory. When the MMO mode is entered the Lock Register appears at all word locations in the device address space. Winbond recommends for future compatibility to read or program the Lock Register only at location 0 of the device address space.

#### 7.5.2 Individual Protection Bits (IPB)

The IPB, Memory Map Overlay (MMO) mode contains a non-volatile bit in each sector in the device. When the mode is entered, the IPB bit for a chosen sector appears in the Least Significant Bit (LSB) of each word in that sector. The non-volatile protection status for that sector is displayed by reading any word location, where the LSB indicates whether or not the sector is protected. The sector is protected against programming and erase operations if the bit is has been programmed to a 0. The sector is not protected by the IPB if the bit has been erased to a 1. Note; there are other features of

the Enhanced Sector Protection (ESP) that can protect sectors. Winbond recommends for future compatibility, to read or program the IPB only at word location 0 of the sector.

#### 7.5.3 IPB Lock

The IPB Lock, Memory Map Overlay (MMO) contains a single volatile bit of memory. Programming or erasing of the IPB is controlled by IPB Lock. IPB is protected against programming and erase operations, if the bit is 0. The IPB is not protected, if the bit is 1. When the IPB Lock mode is entered, the IPB Lock bit appears in the Least Significant Bit (LSB) of each word in the device address space. Winbond recommends for future compatibility, to read or program the IPB Lock only at word location 0 of the device.

#### 7.5.4 Dynamic Protection Bits (DPB)

The DPB Memory Map Overlay (MMO) contains one volatile bit of memory for each Sector. The DPB bit for a sector appears in the Least Significant Bit (LSB) of each word in the sector after entering the DPB mode. Reading any word in a sector displays the protection status for that sector. Sectors are protected during program and erase operations, if the DPB is 0 and unprotected if the bit is 1. Note there are other features of ESP that can protect the sector. Winbond recommends for future compatibility to read, set, or clear the DPB only at word location 0 of the sector.

#### 8 FUNCTIONAL DESCRIPTIONS

#### 8.1 Read

#### 8.1.1 Random Read

The memory device is selected by driving Chip Enable (#CE) LOW and the device will leave the Standby mode. If Write Enable (#WE) is disabled, driven HIGH while #CE is LOW, a random read operation is started. The particular data output will depends on the MMO mode and the specific address provided.

The data output is presented on DQ15-DQ0 when #CE is LOW, Output Enable (#OE) is LOW, #WE is HIGH, address is stable, and the asynchronous access times are met. The Address access time (tacc) is defined to be equal to the delay from stable addresses to valid output data. The chip enable access time (tce) is defined as the delay from a stable #CE to valid data on the outputs. The #OE signal must be LOW for at least the period of the output enable time (toe), before valid read data is available at the outputs.

Device outputs will provide valid read data from the currently active address map mode at the end of the random read access time from address stable (tacc), #OE active (toE), or #CE active (tcE), whichever happens last.

A list of other transitional states during Random Read operation;

- A new random read access begins if #CE remains LOW and any Address[23:4] signals change to a new value.

- In order to get Back to Back accesses, requires an address change to initiate the second access and #CE to remains LOW between accesses Read mode with Outputs Disable, If #CE remains LOW and #OE goes .

- Write mode, if #CE remains LOW, #OE goes HIGH, and #WE goes LOW.

- Standby mode, if #CE returns HIGH.

#### 8.1.2 Page Read

As in the Random Read mode, a random read access sequence is required. Then if #CE remains LOW, #OE remains LOW, Address[23:4] signals remains unchanged, and any of the Address[3:0] signals have change, then a new access within the same Page (32-byte) begins with data appearing on DQ15-DQ0. The Page Read is much faster (tpace) than a Random Read access. If #CE goes HIGH and returns LOW for another access, a random read access is performed and time is required (tacc or tce).

#### 8.2 Device Reset Operations

The Hardware Reset (#RESET) input pin provides a hardware method of resetting the device to a standby mode. Immediately after issuing a Hardware Reset, driving #RESET LOW for at least a period of trp:

- Any operations in progress are terminated,

- Memory Map Overlays (MMO) is exited.

- All outputs are set to HIGH-Z.

- The Status Register is reset.

- The Write State Controller goes to the standby mode.

- #CE is ignored for a period of (tRPH), during the reset operation.

- #CE must be held HIGH to meet the Reset current specification (ICC5).

Note: An operation that was interrupted should be reinitiated to ensure data integrity. An operation command sequence should be executed once the device is ready.

Publication Release Date: Jul 02, 2014

### 8.3 Standby Mode

Standby is the default, minimum power condition while the device is not selected (#CE = HIGH). All inputs are ignored in this mode and all outputs, except RY/#BY are at HIGH-Z. The Write State Controller direct output of the RY/#BY determines its state and is not controlled by other devices or interfaces.

#### 8.4 Automatic Sleep

When addresses remain stable for tACC + 30 ns, the device will automatically enter the Auto Sleep mode and latches the output data. Data on the output pins depends on the level of the #OE signal. The automatic sleep mode is designed to reduce device interface current (Icc6). #OE signal levels are independent of the automatic sleep mode current. The automatic sleep mode current (Icc6) specifications can be found in the *DC Characteristics Tables*.

It's important to note that slow clock durations help reduce current consumption when the Automatic Sleep mode goes active. During slow clock periods, read and write cycles may extend many times their length versus when the clock is operating at high speed. Even when the chip enable is LOW throughout these extended data transfer cycles, the memory device Command State Machine (CSM) will enter the Automatic Sleep mode. This keeps the device in the Automatic Sleep power level for most of the extended duration of the data transfer cycles. Obviously this method is beneficial rather than consuming full read power all the time that the device is selected.

Note, the Write State Controller operates independent of the automatic sleep mode of the Command State Machine (CSM) and will continue to draw current during an active Internal Algorithm. Only when both entities are in their standby modes is the standby level current minimized.

## 8.5 Output Disable Mode

When the #CE signal is driven LOW, either a controlled read or write data transfer may begin. When there is a period at the start of a data transfer when Chip Enable is LOW, Address has become valid, #WE is HIGH and Output Enable (#OE) is HIGH. During this point a Random Read process is started while the data outputs remain at HIGH-Z (Output Disabled). Driving the #OE signal LOW, the device interface transitions to the Random Read mode and output data is actively driven. If in the event the Write Enable (#WE) signal is driven LOW, the device interface transitions to the Write mode. The host system interface should never drive #OE and #WE LOW at the same time; this will prevent conflicts with the device.

## 8.6 Program Methods

#### 8.6.1 Asynchronous Write

When #WE goes LOW after CE is LOW, there is a transition from one of the read modes to the Write mode. If #WE is LOW before #CE goes LOW, there is a transition from the Standby mode directly to the Write mode without beginning a read access. At this point setting Output Enable (#OE) HIGH will start a write data transfer.

Address is captured by the falling edge of #WE or #CE, whichever occurs last. Data is captured by the rising edge of #WE or #CE, whichever occurs first.

A #WE controlled Write access is when the #CE goes LOW before #WE goes LOW and stays LOW after #WE goes HIGH. When #WE are HIGH and #CE goes HIGH, there is a transition to the Standby mode. If #CE remains LOW and #WE goes HIGH, there is a transition to the Read with Output Disable state.

A #CE controlled write mode is when #WE is LOW before #CE goes LOW, the write transfer is started by #CE going LOW. Then if #WE goes LOW after #CE goes HIGH, the address and data is latch by the rising edge of #CE.

Another #CE controlled write mode access is when #WE is LOW before #CE goes LOW and remains LOW after #CE goes HIGH. This is a #CE controlled Write transitions to the Standby mode.

An address change is required to initiate a Read access following a Write access, if #CE remains LOW between accesses.

An address change is required to initiate the second write access in a Back to Back write in which #CE remains LOW between accesses.

The Write State Controller command memory array is not readable by the host system and has no MMO. Its purpose is to examine the address and data in each write transfer to determine if the write is a legal command sequence. If the command sequence is correct, the Write State Controller will initiate the appropriate Internal Algorithms.

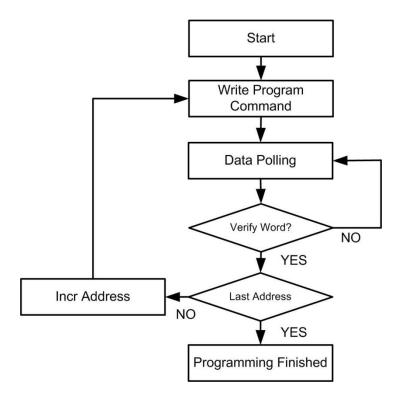

#### 8.6.2 Word Programming

Word programming programs a single word anywhere in the Main Memory Array.

The Word Programming command is a four write cycle sequence. This is done by writing the unlock write command in the first two cycles, a program set up command in the third cycle and finally, in the

fourth cycle the program address and data are written. This will initiate the Internal Word Program algorithm. No further input controls are required. The Internal Algorithm generates all the programming pulses and programmed cell verifications. When the Internal Word Program algorithm is complete, the Write State Controller then returns to its standby mode.

Program operation status can be determined by monitoring the RY/#BY output, reading the Status Register, or by using Data Polling Status.

Program Suspend is the only command that can be written to the device during the Internal Program Algorithm, all others are ignored. However, a hardware reset (#RESET =  $V_{IL}$ ) will immediately terminates the programming operation. Then after transmittening, returns the device to read mode. It is recommended to reinitiate the Word Program command sequence after the device has completed the hardware reset operation to insure data integrity.

The Security Sector Region (SSR) mode may also use the Word Programming command when is entered.

The Word Programming command has a modified version without unlock write cycles when it is used for programming the Lock Register and IPB MMOs. The same command is also used to change volatile bits when entered in to the IPB Lock, and DPB MMOs. See the *Instruction Definition Tables* for program command sequences.

**Figure 8-1 Word Program Operation**

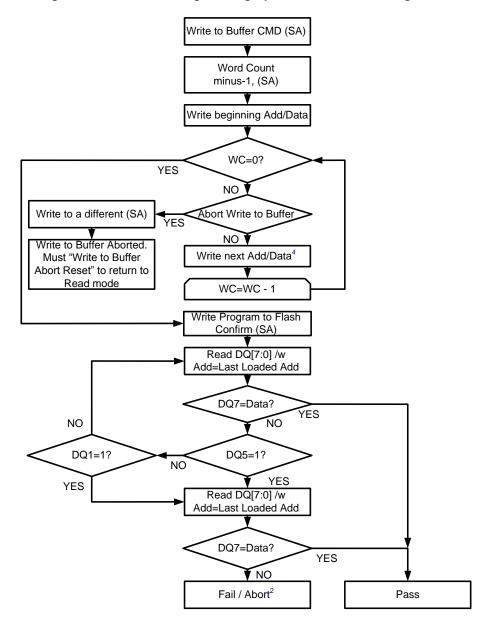

#### 8.6.3 Write Buffer Programming

A 512-byte address range write buffer is used to program data within an aligned 512-byte boundary Line, (example, addresses: 100h to 1FFh). Hence, a Write Buffer Programming operation must be setup on a Line boundary. If the Programming operation is less than 512-bytes, it may start on any word boundary, but may not cross a Write-Buffer-Line boundary. All bit locations in the buffer at the start of a Write Buffer programming operation are in the One's state (FFFFh/Word). Thus, any locations not loaded will retain the existing data.

The Main Memory Array and the Secure Sector Region (SSR) are the areas that are supported by the Write Buffer Programming operation. It is possible to program from 1 bit, up to 512 bytes in one Write Buffer Programming operation. The recommended write buffer method is to only write each page once in a multi-page scenario. Programming should be done in full Lines of 512 bytes setup on 512byte boundaries, for the very best performance.

To initiate a Write Buffer Programming operation, the first 2 cycles are the unlock write commands. The 3<sup>rd</sup> write cycle contains the Write to Buffer command with the program targeted Sector Address (SA). The fourth cycle is to write the number of planned word locations minus 1. This will indicate the Publication Release Date: Jul 02, 2014

number of write buffer addresses that are to be loaded with data. This also indicates when to expect the Program Buffer to flash confirm command. The Write to Buffer command and the Write Word Count command Sector Addresses must match. In order to program, the sector must be unlocked (unprotected).

Cycle 5, the starting address / data combination is written. This will be the first address / data pair to be programmed, and selects the write-buffer-Line address. The operation will abort and return to the initiating state if the Sector Address does not match the Write to Buffer Sector Address. In the following cycles, each address / data pairs must be in sequential order and all write buffer addresses must be within the same Line, otherwise the operation will abort and return to the initiating state.

For each data write operation, the WC counter will decrement and every write is data being loaded into the write buffer. During the write buffer loading period no commands are accepted. The only way to stop writing data to the write buffer is to abort the Write to Buffer command. This is done by writing an invalid address that is outside the Write Buffer Line of the programming operation.

The Program Buffer to Flash command must be issued immediately after the specified number of write buffer locations has been loaded at the sector address. At this point the program algorithm starts and the device status will be busy. The Internal Program Algorithm will program and verifies the data that has been programmed into the selected sector of the Main Memory Array. No control signals or timing parameters during this internal operation is required. The operation will abort and return to the initiating state anytime an incorrect number of write buffer locations have been loaded. The abort occurs because anything other than the expect Program Buffer to Flash command happened at the end of the word count.

The write-buffer internal programming operation can be suspended using the Program Suspend command. When the Internal Program Algorithm is complete, the Write State Controller then returns to the Write State Controller standby mode where the programming operation was started.

Under the following conditions the Write Buffer Programming sequence will be aborted:

- The Word Count cannot exceed a value greater than the buffer size, which is 255 (256 minus 1).

- The Write to Buffer command cannot contain an address that is outside the Line.

- After the Write Word Count number of data words is loaded the Program Buffer to Flash command is not issued

Data Polling Status, reading the Status Register, or monitoring the RY/#BY output can determine the status of the program operation. An abort of the Write Buffer command will occur immediately after an invalid condition, and will indicate a Program Fail in the Status Register at Program Status Bit (Bit

Publication Release Date: Jul 02, 2014

4=1), because of the Write Buffer Abort Status Bit (Bit 3) equals 1. A Clear Status Register command may be issued to clear the Program Status Bit or the next successful program operation will clear the failure status bit.

Caution should be taken when stopping the Write Buffer Programming Sequence by the following methods: Power cycling the device or a Hardware Reset. Using either of these methods may leave the area being programmed in an unknown state with unstable or invalid data. If this is the case reprogrammed with the same data or performing an erased to ensure data values are properly programmed or erased.

# winbond

Figure 8-2 Write Buffer Programming Operation with Data Polling Status

#### Notes:

- 1. DQ7 should be rechecked even if DQ5 = 1 because DQ7 may change simultaneously with DQ5.

- 2. If this flowchart location was reached because DQ5 = 1, then the device FAILED. If this flowchart location was reached because DQ1 = 1, then the Write Buffer operation was ABORTED. In either case the proper RESET command must be written to the device to return the device to READ mode. Write-Buffer-Programming-Abort-Rest if DQ1 = 1, either Software RESET or Write-Buffer-Programming-Abort-Reset if DQ5 = 1.

- 3. See Instruction Definitions Tables for the command sequence as required for Write Buffer Programming.

- 4. When Sector Address is specified, any address in the selected sector is acceptable. However, when loading Write-Buffer address locations with data, all addresses MUST fall within the selected Write-Buffer Page.

# sees winbond

Figure 8-3 Write Buffer Programming Operation with Status Register

#### Notes:

- 1. See Instruction Definitions Tables for the command sequence as required for Write Buffer Programming.

- When Sector Address is specified, any address in the selected sector is acceptable. However, when loading Write-Buffer address locations with data, all addresses MUST fall within the selected Write-Buffer Page.

**Table 8-1 Write Buffer Programming Command Sequence**

| Address             | Data  | Sequence                                        | Comment                                                                                                            |

|---------------------|-------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 555 AA              |       | Unlock Command 1.                               |                                                                                                                    |

| 2AA 55              |       | Unlock Command 2.                               |                                                                                                                    |

| SA 0025             |       | Write to Buffer Command at Sector Address.      |                                                                                                                    |

| SA WC               |       | Number of Locations at Sector Address.          | WC = number of words to program minus 1                                                                            |

|                     |       | WC set to $1 = 2$ words to program.             | Example                                                                                                            |

| Starting<br>Address | PD    | Write Starting Address / Data pair.             | Selects Write-Buffer-Page and loads first Address/Data Pair.                                                       |

| WBL                 | PD    | Write next Address / Data pair.                 | All addresses MUST be within the selected write-buffer-page boundaries, and have to be loaded in sequential order. |

| WBL                 | PD    | Write LAST Address/Data pair.                   | All addresses MUST be within the selected write-buffer-page boundaries, and have to be loaded in sequential order. |

| SA                  | 0029h | Write Buffer Program Confirm at Sector Address. | This command MUST follow the last write buffer location loaded, or the operation will ABORT.                       |

|                     |       | Device goes busy.                               |                                                                                                                    |

#### Legend:

SA = Sector Address (Non-Sector Address bits are don't care. Any address within the Sector is sufficient.)

WBL = Write Buffer Location (MUST be within the boundaries of the Write-Buffer-Line specified by the Starting Address.)

WC =Word Count

PD = Program Data

## 8.7 Program Suspend / Program Resume Commands

An internal programming operation can be interrupted so that data can read from any non-suspended Boundary Line by using the Program Suspend command. During a programming process and the Program Suspend command is written, the programming operation will halt within the period of test and the status bits will be updated. When writing the Program Suspend command addresses are don't care.

Program Suspend has two commands available; The Erase/Program suspend command (B0h command code), which is a combined legacy command. The Program Suspend command (51h

30

command code). Program resume also has two possible commands; The Erase / Program resume command (30h command code) legacy combined command. Program Resume command (50h command code). It is recommended not to use the combine Erase/Program suspend or the combined Erase/Program resume commands for programming and for the erase suspend and resume use the legacy combined commands.

After suspending the programming operation, any non-suspended Line of array data can be read. If during an Erase Suspended operation to start a Programming operation that was suspended, only addresses not in the Erase or Program Suspend may be read.

The device returns back to program operation and the status bits are updated after the Program Resume command is executed. Monitoring the Status Register or using the Data Polling method, the programming operation status can be determined.

During Program Suspend, valid accesses and commands:

- Any non-erase suspended sector can be Read

- Any non-program suspended Line can be Read.

- Status Read command

- Exit MMO or Command Set Exit

- Program Resume command

Program Resume command must be executed to exit the Program Suspend mode to continue the programming operation. Resume commands are ignored once the device has returned to the programming operation. After the device has resumed programming operation a Program Suspend command can be re-written.

Programming operations can be interrupted as often as necessary but, the minimum requirement between a Program Resume and the next Program Suspend must be greater than or equal to tprs.

Not supported is Program suspend and resume mode while entered in an MMO. Likewise, there is no support while in program suspend to enter into MMO.

#### 8.8 Erase Methods

#### 8.8.1 Chip Erase

The entire Main Memory Array is erased by chip erase function. The Internal Erase Algorithm will first program and verifies the entire memory prior to an electrical erase. All locations within the device will contain FFFFh after a successful chip erase. There is no need to provide any control signals or timing parameters during this operation. Initiating the chip erase command sequence requires writing two

unlock cycles, the a setup command cycle, two additional unlock write cycles and then the chip erase command, which in turn actives the Internal Erase Algorithm.

While the Internal Erase operation is in progress, no data can be read from the device. Chip Erase operation status can be determined by reading the Status Register or using Data Polling. Only a Status Read, Hardware RESET or Power cycle are valid, once the chip erase operation has begun, ignoring all other commands. When the Internal Erase Algorithm has finished, the Write State Controller will return to the standby mode. However, in the case of a Hardware Reset or Power Cycle, the erase operation immediately terminates and returns to read mode after a period of treh. In the event the chip erase operation is terminated and to insure the integrity of the device data, the chip erase command sequence should be reinitiated once the device has returned to an idle state.

If a sector is protected during chip erase, the Internal Erase Algorithm will ignore the protected sector and move on to the next sector erase.

#### 8.8.2 Sector Erase

The sector erase function erases a selected 128-kbyte sector in the main memory array. The Internal Erase Algorithm programs and verifies the select sector prior to an electrical erase. There are no requirements for any control signals or timing parameters during this internal operation. All locations within the erased sector will contain an FFFFh pattern, indicating a successful sector erase. If the sector has been protected, the sector will not be erased. Reading the Status Register or using Data Polling can be used to determine the status of the erase operation. It takes six cycles to perform a sector erase command sequence; writing two unlock cycles, followed by a setup command, writing two more unlock cycles, and the sector erase command that contains the address of the desired sector to be erased.

The Status Register Read and Erase Suspend commands are the only valid commands that can be used after the sector erase operation has commenced, ignoring all other commands. The sector erase operation and be terminated abruptly by a hardware reset at which time the device returns to read mode after a period traph. If this is the case, the sector erase command procedure must be redone again once the device has completed the reset operation to ensure integrity of the data.

Figure 8-4 Sector Erase operation

## 8.9 Erase Suspend / Erase Resume

The Erase Suspend command interrupts a sector erase operation making it possible to read data or program data in the main memory array. The Erase Suspend command is valid when a sector erase or a program operation is in progress. Executing an Erase Suspend command during a chip erase operation will be ignored. The device requires a maximum of test to suspend the erase operation and update the status bits any time the Erase Suspend command is executed during the a sector erase operation.

Once in the erase-suspend mode, the Main Memory Array can be read or programmed. Reading at any address outside erase-suspended sectors produces valid data. Reading within the suspended sectors will result in invalid data. Monitoring the Status Register or Data Polling can be used to determine the status of the device actively performing an erase or erase-suspended function.

The Write State Controller will return the device back to the erase-suspend mode after a program operation has completed that was called from the erase suspend mode. The status of the program operation can be determined by reading the Status Register, the same as in the standard program operation.

In the event there is a program failure during an Erase Suspend operation, it is necessary to initiate a Clear or Reset command to return the device to the Erase Suspended mode. Before trying another program operation on the main memory array, the erase function will need to be resumed and completed.

During Erase Suspend, valid accesses and commands:

- Any other non-suspended sector can be read.

- Any other non-suspended sector can be programmed.

- Status Read command

- Enter DPB MMO

- DPB Set

- DPB Clear

- DPB Status Read

- Exit MMO or Command Set Exit

- Erase Resume command

To resume the sector erase operation, an Erase Resume command must be executed. The device will return back to erasing at which point the status bits will be updated. If another Erase Resume is attempted it will be ignored. Once the device has resumed erase operation another Erase Suspend command can be initiated.

While entered in an MMO, Erase Suspend and Resume is not supported. Likewise, entry into a MMO while an erase suspend is not supported.

#### 8.10 Blank Check

To confirm if a selected sector is erased a Blank Check command should be used. Reads to the main memory array are not supported during a Blank Check operation. Trying to do so will return unknown data. To execute a Blank Check operation on a specific Sector, write the address (SA)555 and the data 33h after the Write State Controller is in the standby mode.

If the device is in a programming or erase mode of operation a Blank Check command cannot be written.

The Status Register can confirm if the device is still busy and when it has completed the Blank Check operation, whether or not the sector is blank. Bit 7, Device Ready Bit of the Status Register will show if a Blank Check is being performed by the device. Bit 5, Erase Status Bit of the Status Register will indicate an erased sector when reading a '0' or a non erased sector when reading a '1'. The device will immediately halt the Blank Check operation and update the status as soon as any bit in the selected sector is found not to be erased.

The Write State Controller will return to the Standby mode, as soon as the Blank Check is completed.

#### 8.11 Enhanced Sector Protection Methods

#### 8.11.1 Enhanced Sector Protection (ESP)

Enhanced Sector Protection is a method used to enable or disable program and erase operations, in any or all sectors. Described in the section are the various methods of protecting data stored in the main memory array. An outline of these methods is shown in the following figure.

Figure 8-5 Enhanced Sector Protection IPB Program Algorithm

Each sector has a non-volatile Individual Protection Bit (IPB) and a volatile Dynamic Protection Bit (DPB) associated with it. If in either case the bit is 0, the sector becomes protected from both program and erase operations.

Program and erase of the IPB bits are protected when the IPB Lock bit is 0.

The Individual Protection mode (default) clears the IPB Lock to a 1 during a Power Up Reset or Hardware Reset. This is done so that the IPB bits are unprotected after device reset. When needed there is a IPB Lock bit command to write the volatile IPB Lock bit to a 0 to protect the all the IPB. There is no command in the Individual Protection mode to clear the IPB Lock bit to 1 after it is programmed to 0, except for the Power Up Reset or Hardware resets.

The selection of the Individual Protection mode is set at the factory by programming OTP bit in the Lock Register.

When shipped from Winbond, all the sector IPB bits are erased so that all main memory array sectors are unprotected.

## 8.11.2 IPB Lock

This one per device volatile Individual Protection Bit Lock is a bit that will protect all IPB bits. When programmed to 0, it locks all sector IPBs and if the bit is 1, it allows the all sector IPBs to be changed. Only after the sector IPBs are configured to the desired state should the IPB Lock bit be programmed to 0. Note the IPB Lock command can only program the bit to 0.

To erase the IPB Lock bit, only a Power Up Reset or a hardware reset will restore the value to 1 to allow sector IPB bits to be changed. There is no software command operation that can clear the IPB Lock to a 1.

## 8.11.3 Individual Protection Bits (IPB)

The non-volatile Individual Protection Bits (IPB) is located in a separate non-volatile flash array. There is one IPB bit assigned to each sector. When an IPB is 0 their corresponding sectors is protected from program and erase operations. The IPB can be programmed individually, but are erased as a group. Important to note, the Write State Controller takes care of the preprogramming and verification prior to erasure.

When programming an IPB bit the typical word programming time is required. To monitor the operation status of an IPB bit programming or erase, DQ6 Toggle Bit I of the Data Polling Status will toggle until the operation is complete. Note; typical sector erase time is required to erasing all the IPBs.

Program or erase command will not execute and will time-out, if the IPB Lock is equal 0, without programming or erasing the IPB.

The IPB Status Read command can be used to check the protection state of an IPB for a given sector, but you must first enter the IPB MMO mode. See Instruction Definition Tables.

## 8.11.4 Dynamic Protection Bits (DPB)

The volatile Dynamic Protection Bits are exclusive for each sector and can be individually changed. Only sectors that have their IPBs clear to 1 (unprotected) can the DPBs control. By issuing the DPB Set or Clear command sequences, the DPB are clear to 1 or set to 0, thus placing each sector in the

unprotected or protected state respectively. The DPB can be set to 0 or cleared to 1 as often as needed.

## 8.11.5 Sector Protection Bit Status Summary

Sector Protection status base on IPB, DPB and IPB Lock bit weight is as follows:

**Table 8-2 Sector Protection Status**

| Contar Status                           | Sector Protection Bit Status |     |     |  |  |  |  |  |  |  |

|-----------------------------------------|------------------------------|-----|-----|--|--|--|--|--|--|--|

| Sector Status                           | IPB Lock                     | IPB | DPB |  |  |  |  |  |  |  |

| Unprotected: IPB and DPB are changeable | 1                            | 1   | 1   |  |  |  |  |  |  |  |

| Protected: IPB and DPB are changeable   | 1                            | 1   | 0   |  |  |  |  |  |  |  |

| Protected: IPB and DPB are changeable   | 1                            | 0   | 1   |  |  |  |  |  |  |  |

| Protected: IPB and DPB are changeable   | 1                            | 0   | 0   |  |  |  |  |  |  |  |

| Unprotected: DPB is changeable          | 0                            | 1   | 1   |  |  |  |  |  |  |  |

| Protected: DPB is changeable            | 0                            | 1   | 0   |  |  |  |  |  |  |  |

| Protected: DPB is changeable            | 0                            | 0   | 1   |  |  |  |  |  |  |  |

| Protected: DPB is changeable            | 0                            | 0   | 0   |  |  |  |  |  |  |  |

## 8.11.6 Lock Register

The Lock Register is a non-volatile One Time Programmable (OTP) register where the bits control protection of the SSR, and the default Individual Protection Mode, programmed at the factory.

The Security Sector Region (SSR) protection bits are OTP and once programmed (locked); there is no command for unlocking the protected portion of the Security Sector Region. At this point no program or erase operations are allow in the SSR.

The Lock Register programming time is typically the same as word programming. Monitoring Data polling Status DQ6 Toggle Bit I during a Lock Register programming Internal Algorithm will toggle until the operation is finished. Another method to monitor the programming status of the Lock Register can be done reading the Status Register's bit 4 and 7. See *Status Register Operations* for information on these status bits.

The Reserved Bits must be 1 (masked), when programming the Lock Register Bits.

Table 8-3 Lock Register

| Name                  | Bit  | Default Value |

|-----------------------|------|---------------|

| Reserved              | 15-9 | 1             |

| Reserved              | 8    | 0             |

| Reserved              | 7    | X             |

| SSR Customer Lock Bit | 6    | 1             |

| Reserved              | 5    | 1             |

| <b>Estate</b> winbo                         | nd - |   |

|---------------------------------------------|------|---|

| Reserved                                    | 4    | 1 |

| Reserved                                    | 3    | 1 |

| Reserved                                    | 2    | 1 |

| Individual Protection Mode (Factory Locked) | 1    | 0 |

| SSR Factory Lock Bit                        | 0    | 0 |

# 8.12 Security Sector Region

The Security Sector Region (SSR) MMO provides an extra flash memory area that can be programmed once and permanently protected from further changes. The SSR is 1024 bytes in length. It consists of two 512 bytes regions, Factory Locked Security Sector Region and 512 bytes for Customer Locked Security Sector Region.

The Secure Silicon Entry command sequence contains the sector address; this will overlay the Security Sector Region address map on the Main Memory Array selected sector. The overlay starts at location 0 in the selected sector. While the SSR MMO is entered the contents of locations exceeding the maximum SSR MMO address of that sector are consider as undefined data.

**Table 8-4 Security Sector Region**

| Word Address Range    | Content                                | Size       |

|-----------------------|----------------------------------------|------------|

| (SA) + 0000h to 00FFh | Factory Locked Security Sector Region  | 512 bytes  |

| (SA) + 0100h to 01FFh | Customer Locked Security Sector Region | 512 bytes  |

| (SA) + 0200h to FFFFh | Undefined                              | 127 Kbytes |

# 8.13 Monitoring Device Status

Status Register, Data Polling and the Ready/Busy# (RY/#BY) Signal are the three methods for monitoring Internal Algorithms status.

## 8.13.1 Status Register

The Status Register MMO is a 16-bit register that provides status of program and erase operations. The Status Register Read command is a two cycle command. First cycle overlays the contents of the status register in all locations of the device address space. The second cycle reads the information contents of the status register. The Status Register MMO is exited automatically after the read access.

After the status register read access, #CE or #OE must go HIGH for a period of tceph or toeph, respectively to return to the active address space at the time the initial Status Register Read command was executed.

Some of the Status Register bits are associated to the results indicating success / failure of the most recently completed Internal Algorithm, while remaining bits are for current status of an Internal Algorithm that is in progress, suspended or has completed.

The upper 8 bits DQ[15:8] are reserved. They are undefined bits that should be treated as don't care and ignored. The Clear Status Register Command will turn results related bits to 0, but will not affect the current state bits.

**Table 8-5 Status Register**

| Bit # | Bit Description               | Reset<br>Status | Busy<br>Status | Read Status                                                            |

|-------|-------------------------------|-----------------|----------------|------------------------------------------------------------------------|

| 15:8  | Reserved                      | Χ               | Invalid        | X                                                                      |

| 7     | Device Ready Bit              | 1               | 0              | 1                                                                      |

| 6     | Erase Suspend<br>Status Bit   | 0               | Invalid        | Erase not Suspended=0 Erase is Suspended=1                             |

| 5     | Erase Status Bit              | 0               | Invalid        | Erase successful=0 Erase fail=1                                        |

| 4     | Program Status Bit            | 0               | Invalid        | Program successful=0 Program fail=1                                    |

| 3     | Write Buffer Abort Status Bit | 0               | Invalid        | Program not aborted=0 Program aborted during Write to Buffer command=1 |

| 2     | Program Suspend<br>Status Bit | 0               | Invalid        | No Program in suspension=0 Program in suspension=1                     |

| 1     | Sector Lock Status<br>Bit     | 0               | Invalid        | Sector not locked during operation=0 Sector locked error=1             |

| 0     | Reserved                      | 0               | Invalid        | X                                                                      |

Notes: