# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

#### **General Description**

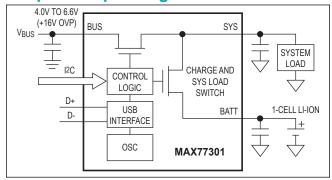

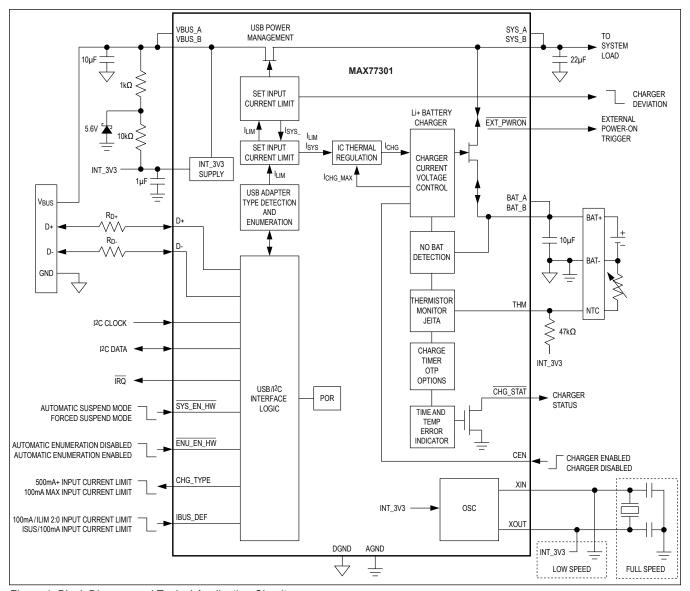

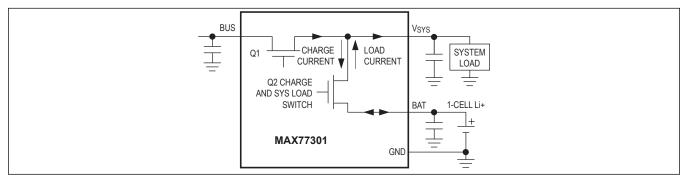

The MAX77301 is a JEITA-compliant\* lithium-ion linear battery charger that operates from a USB port, a dedicated charger, or universal adapter. The IC integrates independent battery charge switch, current sense circuit, MOSFET pass elements, thermal regulation circuitry, and eliminates the external reverse-blocking Schottky diode to create the simplest and smallest USB-compliant charging solution.

The IC includes automated detection of charge adapter type, making it possible to distinguish USB 2.0 device, USB charger, dedicated charger devices as well as standard input adapters. When enumeration is enabled, the IC automatically negotiates with a USB host, making it possible to achieve the highest-charging current available from a USB 2.0 device or USB charger without processor intervention. The adapter type detection is compliant with USB 2.0 as well as battery charging Specification Revision 1.1.

The IC controls the charging sequence for single-cell Li+ batteries from battery detection, prequalification, fast charge, top-off, and charge termination. Charging is controlled using constant current, constant voltage and constant die-temperature (CCCVCTj) regulation for safe operation under all conditions. The IC is also compliant with JEITA battery charging requirements.

The Smart Power Selector feature makes the best use of limited USB or adapter power. Battery charge current is set independent of the input current limit. Power not used by the system charges the battery. The battery assists the input source when needed. System voltage is maintained by allowing the application to operate without a battery, a discharged battery, or a dead battery. Automatic input selection switches the system from battery to external power.

The I<sup>2</sup>C interface provides full programmability of battery charge characteristics, input current limit, and protection features. This provides flexibility for use with a wide range of adapter and battery sizes.

Other features include undervoltage lockout (UVLO), overvoltage protection (OVP), charge status and fault flags, input power-OK monitor, charge timer, 3.3V/10mA auxiliary output, and an external power-on switch.

### **Applications**

- Smartphones, Bluetooth Headsets

AR/VR Glasses

- · Hearables. Wearables · Portable Devices

#### **Benefits and Features**

- Enables Charging from a USB Port

- Automatic Detection of Adapter Type

- Input Current Up to 1500mA and Charging Current Up to 900mA

- Enumeration Without Processor Intervention

- Supports USB Low-Speed and Full-Speed

- Compliant with USB 2.0 Specification and Battery Charging Specification (Revision 1.1)

- Compliant with Next Generation Low-Voltage Li-Ion Battery Profiles

- Input Overvoltage Protection Up to 16V

- Smart Power Selector<sup>™</sup> Allows Power Path Operation with Discharged or No Battery

- Battery Detection Including Packs with Open Protectors

- Thermal Regulation Prevents Overheating

- LED Indicator for Charge Done, Precharge, and Time/ Temperature Error

- Serial (400kHz) I<sup>2</sup>C-Compatible Interface

- 6μA (typ) Shutdown Current

- 2.44mm x 2.44mm, 25-Bump WLP Package

Ordering Information appears at end of data sheet.

#### **Simplified Operating Circuit**

Smart Power Selector is a trademark of Maxim Integrated Products. Inc.

\*U.S. Patent # 6,507,172

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

#### **TABLE OF CONTENTS**

| General Description                |    |

|------------------------------------|----|

| Applications                       | 1  |

| Benefits and Features              | 1  |

| Simplified Operating Circuit       | 1  |

| Absolute Maximum Ratings           | 6  |

| Package Information                | 6  |

| WLP                                | 6  |

| Electrical Characteristics         | 6  |

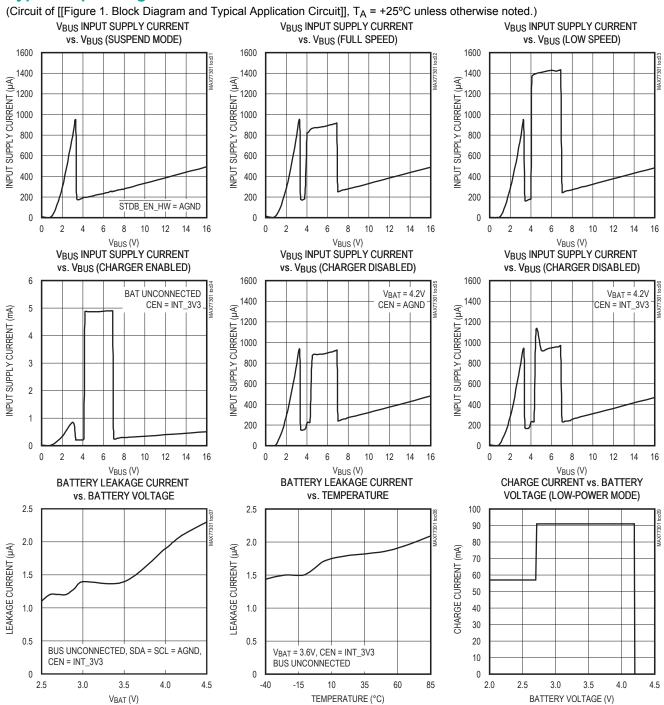

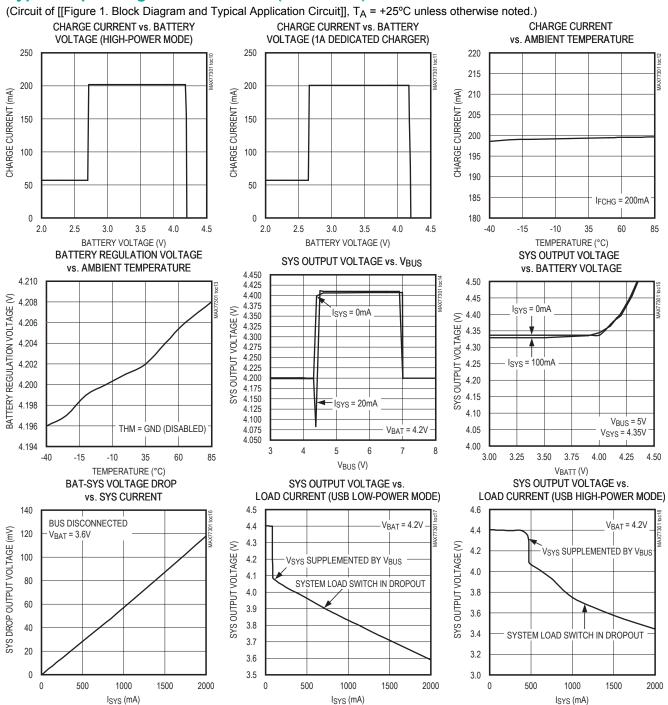

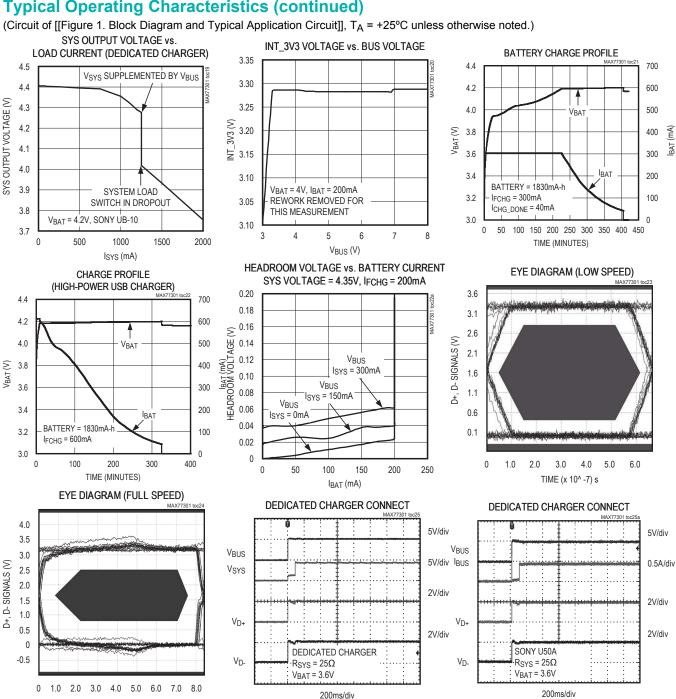

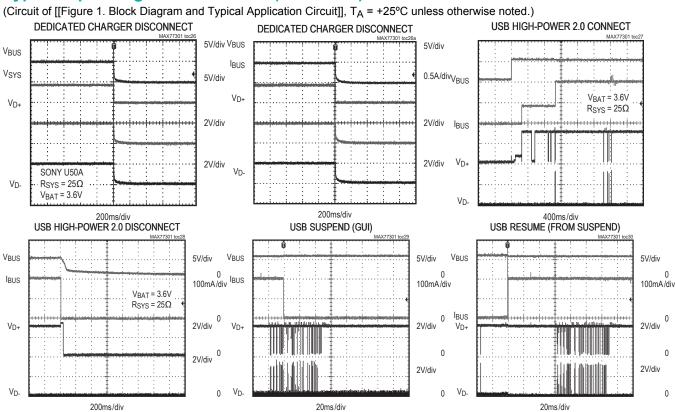

| Typical Operating Characteristics  | 15 |

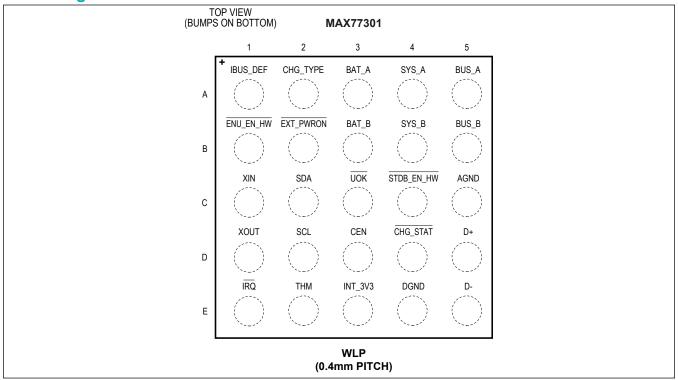

| Pin Configuration                  | 19 |

| Pin Description                    | 19 |

| Detailed Description               | 22 |

| Overview                           | 23 |

| Data Contact Detection             | 23 |

| Power-On Reset                     | 23 |

| Interrupt Request (IRQ)            | 23 |

| USB Interface                      | 24 |

| D+ and D                           | 26 |

| Low/Full Speed                     | 26 |

| Adapter Detection                  | 26 |

| Low-Power Mode                     |    |

| USB Suspend                        | 27 |

| Keyboard Test Mode                 | 29 |

| Wake-Up and USB Resume             | 30 |

| USB Enumeration                    | 30 |

| Smart Power Selector               |    |

| System Load Switch                 |    |

| Input Limiter                      |    |

| Setting Input Current Limit        |    |

| Minimum V <sub>SYS</sub> Threshold |    |

| Input Current Limit                |    |

| Power Monitor Output (UOK)         |    |

| Soft-Start                         |    |

| Battery Charger                    |    |

| Charge Enable                      | 39 |

| Charge Termination (EOC)           | 40 |

| CHG_TYPE                           | 40 |

| IBUS_DEF                           | 40 |

| Charge Status (CHG STAT)           | 40 |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

## TABLE OF CONTENTS (CONTINUED)

|    | ` ,                                     |      |

|----|-----------------------------------------|------|

|    | Battery Detection                       | . 41 |

|    | Automatic Detection Mode                | . 42 |

|    | NTC Detection Mode                      | . 43 |

|    | Thermistor Input (THM)                  | . 43 |

|    | Thermal Overload Protection             | . 44 |

|    | External Clock (Full Speed Only)        | . 44 |

|    | USB Low-Speed Operation                 | . 44 |

|    | External Crystal or Ceramic Resonator   | . 44 |

|    | External Clock                          | . 44 |

|    | Clock Timing Accuracy                   | . 45 |

|    | External Power-On Signal                | . 45 |

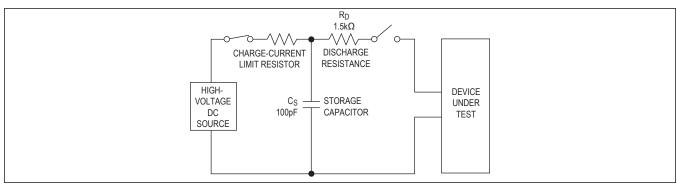

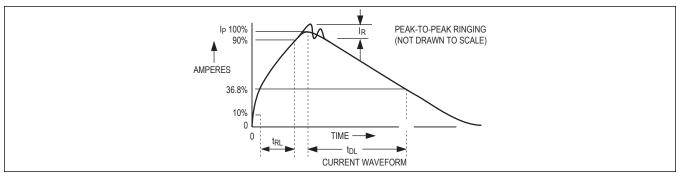

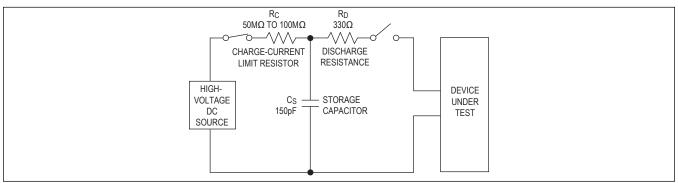

|    | ESD Protection                          | . 45 |

|    | ESD Test Conditions                     | . 46 |

|    | IEC 61000-4-2                           | . 47 |

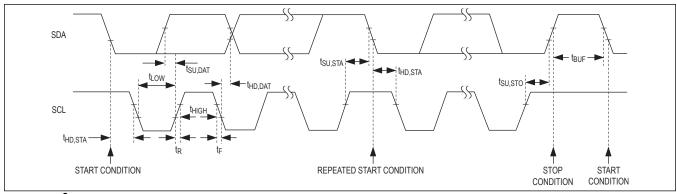

|    | I <sup>2</sup> C Functional Description | . 47 |

|    | I <sup>2</sup> C Slave Address          | . 48 |

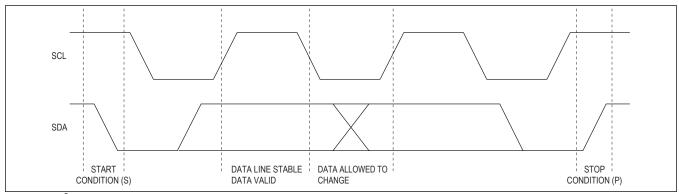

|    | I <sup>2</sup> C Bit Transfer           | . 48 |

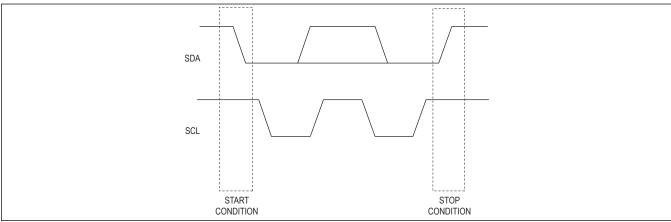

|    | START and STOP Conditions               | . 49 |

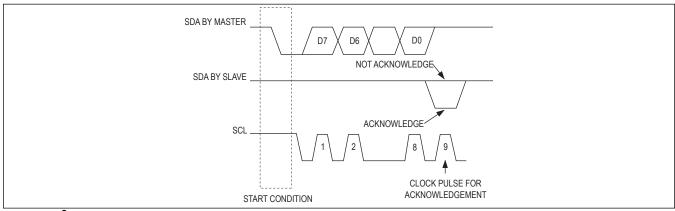

|    | Acknowledge                             | . 49 |

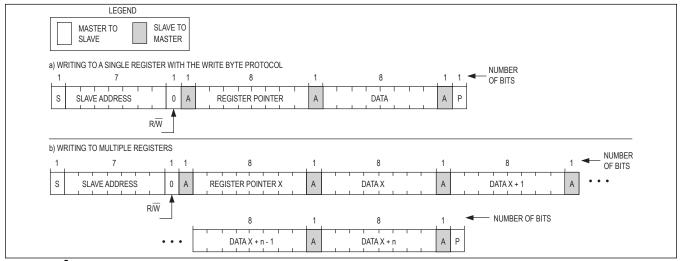

|    | Write Operations                        | . 50 |

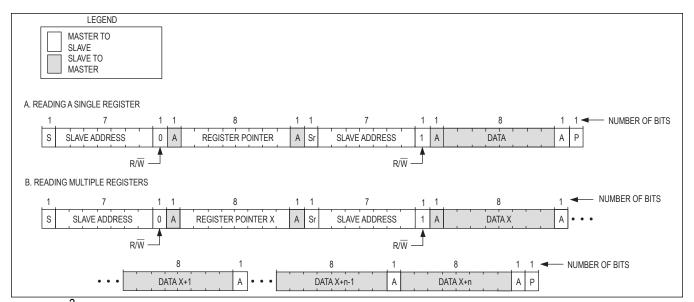

|    | Read Operations                         | . 51 |

|    | dering Information                      |      |

| Re | vision History                          | . 67 |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

### LIST OF FIGURES

| Figure 1. Block Diagram and Typical Application Circuit | 22 |

|---------------------------------------------------------|----|

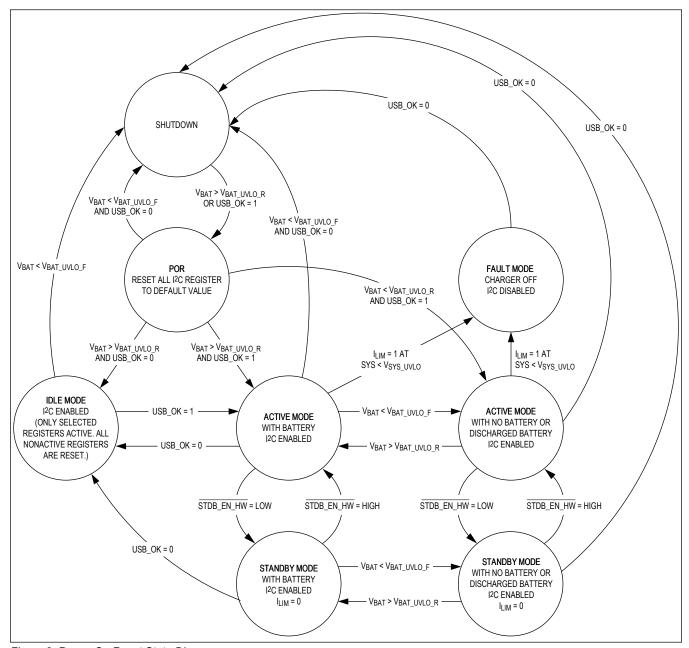

| Figure 2. Power-On Reset State Diagram                  |    |

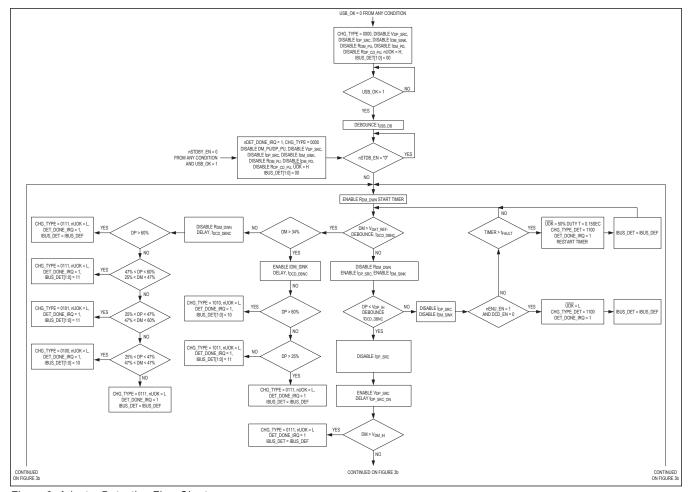

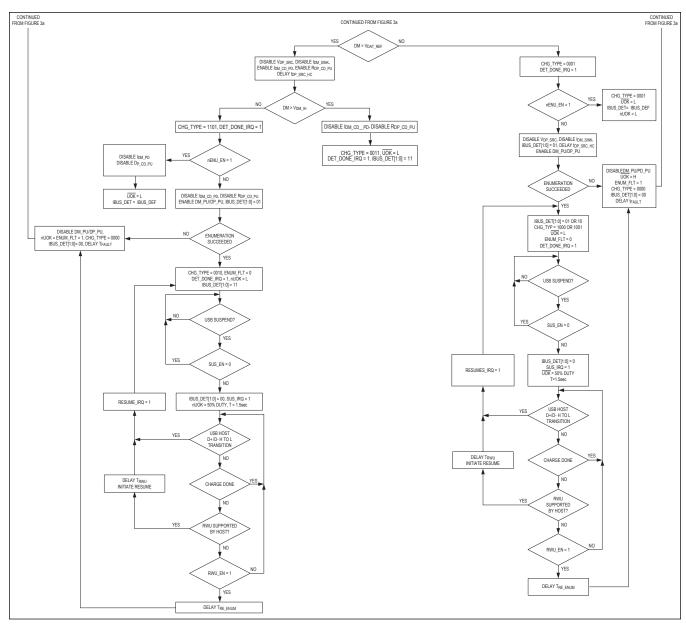

| Figure 3. Adapter Detection Flow Chart                  |    |

| Figure 4. Adapter Detection Flow Chart                  |    |

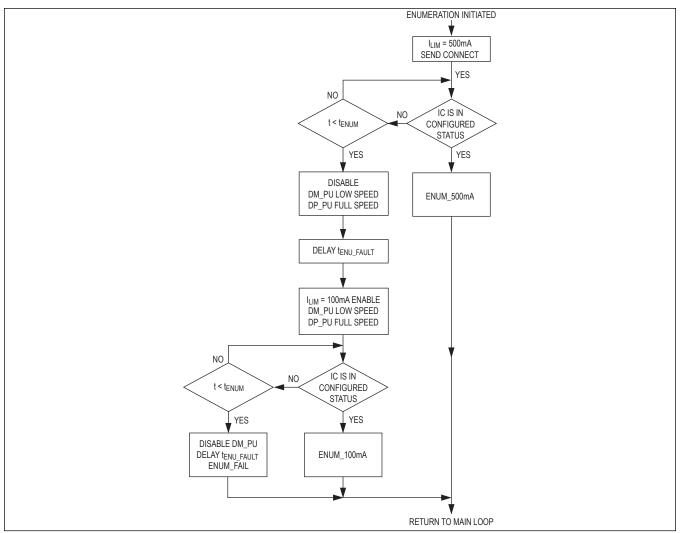

| Figure 5. Enumeration Flow Chart                        |    |

| Figure 6. USB BUS Traffic: Low-Speed Enumeration        |    |

| Figure 7. USB BUS Traffic: Full-Speed Enumeration       |    |

| Figure 8. Smart Power Selector Block Diagram            |    |

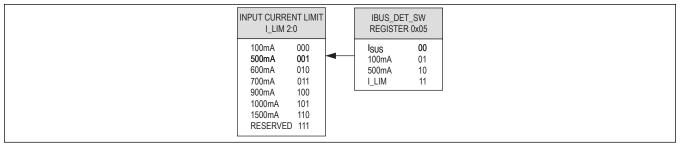

| Figure 9. Input Current Limit Settings                  |    |

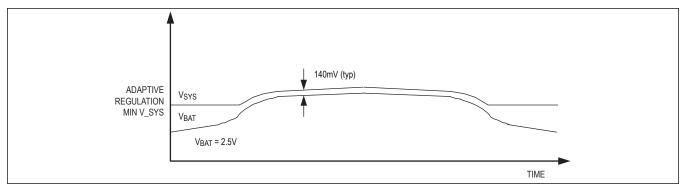

| Figure 10. SYS Regulation                               |    |

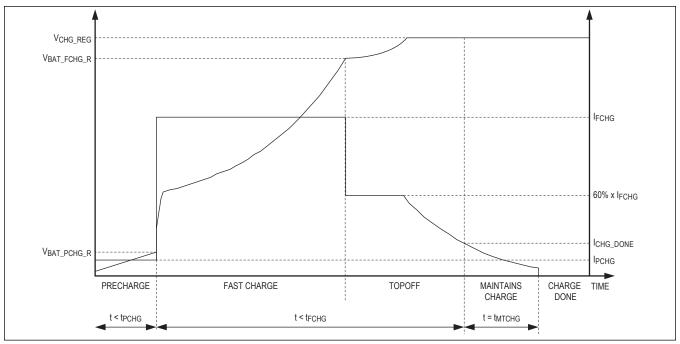

| Figure 11. Charge Profile                               |    |

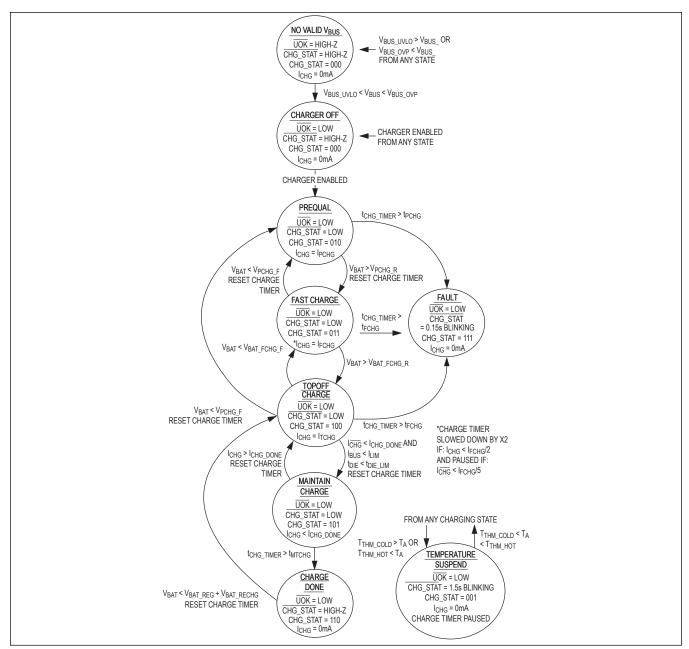

| Figure 12. Charger State Diagram                        |    |

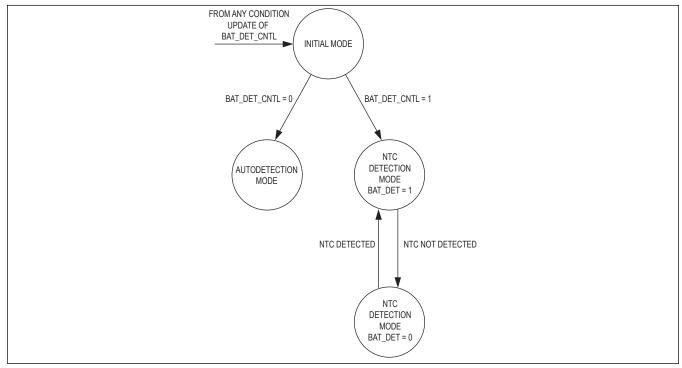

| Figure 13. Battery Detection State Diagram              |    |

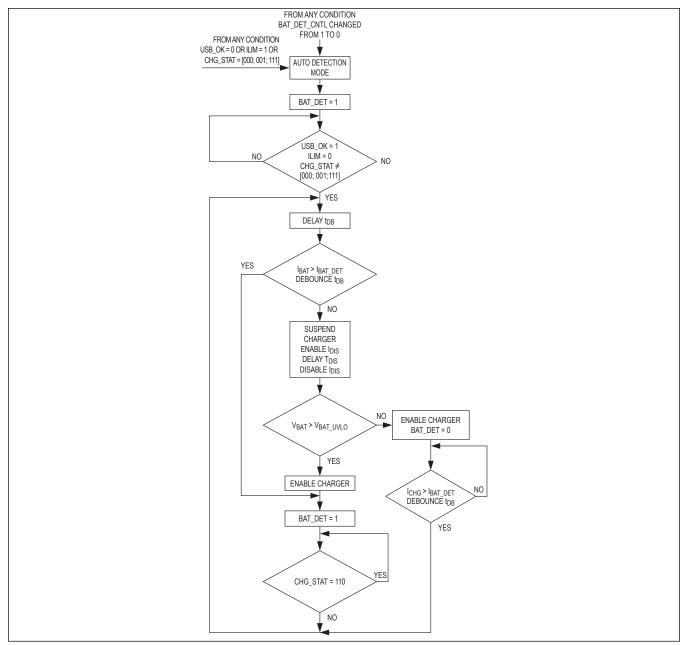

| Figure 14. Battery Present Flow Chart                   |    |

| Figure 15. JEITA Battery Safety Regions                 |    |

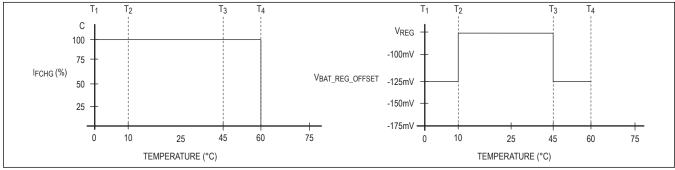

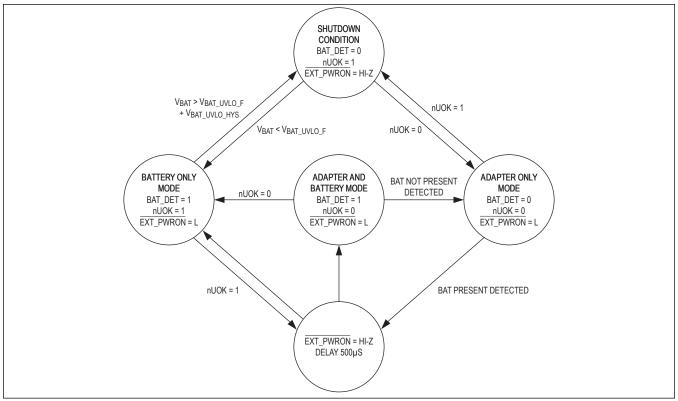

| Figure 16. EXT_PWRON State Diagram                      |    |

| Figure 17. Human Body ESD Test Models                   |    |

| Figure 18. Human Body Model Current Waveform            |    |

| Figure 19. IEC61000-4-2 ESD Test Model                  |    |

| Figure 20. I <sup>2</sup> C Interface Timing Diagram    |    |

| Figure 21. I <sup>2</sup> C Bit Transfer                |    |

| Figure 22. I <sup>2</sup> C START and STOP Conditions   |    |

| Figure 23. I <sup>2</sup> C Acknowledge                 |    |

| Figure 24. I <sup>2</sup> C Write Operations            |    |

| Figure 25. I <sup>2</sup> C Read Operations             | 51 |

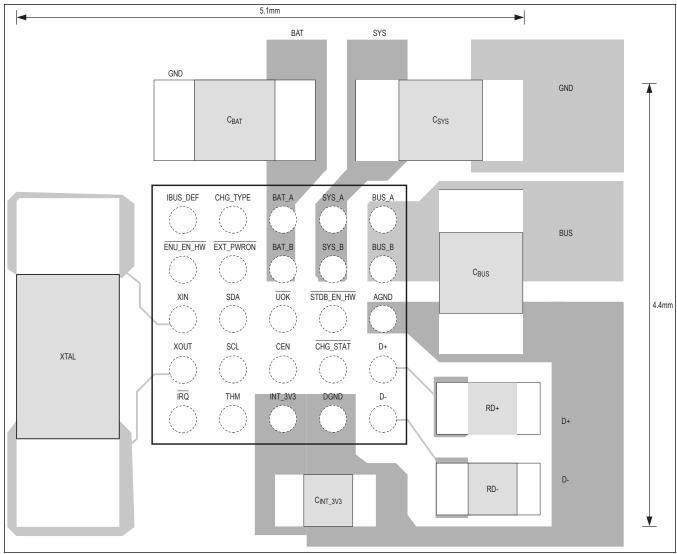

| Figure 26. Recommended PCB Layout for Full Speed        | 64 |

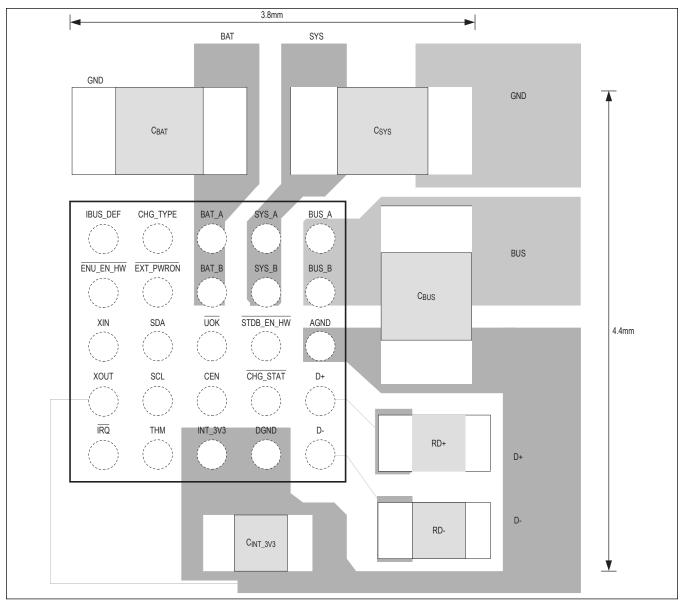

| Figure 27. Recommended PCB Layout for Low Speed         |    |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

#### **LIST OF TABLES**

| Table 1. Status Registers                            | 25 |

|------------------------------------------------------|----|

| Table 2. Adapter Type                                | 25 |

| Table 3. Device Descriptor                           | 33 |

| Table 4. V <sub>BUS</sub> Valid Input Range (Rising) | 36 |

| Table 5. UOK States                                  | 37 |

| Table 6. CHG_TYPE                                    | 40 |

| Table 7. IBUS_DEF                                    | 40 |

| Table 8. CHG_STAT Output                             | 40 |

| Table 9. I <sup>2</sup> C Register Map               | 52 |

| Table 10. CHIP_ID (Register 0x00)                    | 53 |

| Table 11. CHIP_REV (Register 0x01)                   | 53 |

| Table 12. STATUS_A (Register 0x02)                   | 53 |

| Table 13. STATUS_B (Register 0x03)                   | 54 |

| Table 14. STATUS_C (Register 0x04)                   | 55 |

| Table 15. EVENT_A (Register 0x05)                    | 55 |

| Table 16. EVENT_B (Register 0x06)                    | 56 |

| Table 17. IRQ_MASK_A (Register 0x07)                 | 56 |

| Table 18. IRQ_MASK_B (Register 0x08)                 | 56 |

| Table 19. USB_CNTL (Register 0x09)                   | 57 |

| Table 20. BAT_CNTL (Register 0x10)                   | 58 |

| Table 21. IBUS_CNTL (Register 0x0A)                  | 58 |

| Table 22. CHARGER_CNTL_A (Register 0x0B)             | 59 |

| Table 23. CHARGER_CNTL_B (Register 0x0C)             | 60 |

| Table 24. CHARGER_TMR (Register 0x0D)                | 60 |

| Table 25. CHARGER_VSET (Register 0x0E)               | 61 |

| Table 26. CHARGER_JEITA (Register 0x0F)              | 61 |

| Table 27. PRODUCT_ID_A (Register 0x11)               | 62 |

| Table 28. PRODUCT_ID_B (Register 0x12)               | 62 |

| Table 29. VENDOR_ID_A (Register 0x13)                | 63 |

| Table 30 VENDOR ID B (Register 0x14)                 | 63 |

## JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

#### **Absolute Maximum Ratings**

| BUS_ to AGND0.3V to +16.0V                                  | I <sub>BUS</sub> and I <sub>SYS</sub> Continuous Current (Note 1) 2200mA <sub>RMS</sub> |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| INT_3V3 to AGND                                             | I <sub>BAT</sub> Continuous Current (Note 1)                                            |

| CHG_TYPE, IBUS_DEF, ENU_EN_HW, IRQ, D+, D-, UOK,            | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) WLP (derate                       |

| CHG_STAT, BAT_, SYS_, CEN, STDB_EN_HW to                    | 19.2mW/°C above +70°C)1538mW                                                            |

| AGND0.3V to +0.6V                                           | Operating Temperature40°C to +85°C                                                      |

| XIN, THM, XOUT, to AGND0.3V to V <sub>INT</sub> _3V3 + 0.3V | Junction Temperature+150°C                                                              |

| EXT_PWRON, SDA, SCL to AGND0.3V to (VSYS + 0.3V             | Storage Temperature Range65°C to +150°C                                                 |

| DGND to AGND0.3V to +0.3V                                   | Soldering Temperature (reflow)+260°C                                                    |

Note 1: IBUS = IBUS A + IBUS B; ISYS = ISYS A + ISYS B; IBAT = IBAT A + IBAT B

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Package Information

#### **WLP**

| Package Type                                              | 25 WLP (0.4mm pitch)           |

|-----------------------------------------------------------|--------------------------------|

| Package Code                                              | W252H2+1                       |

| Outline Number                                            | <u>21-0453</u>                 |

| Land Pattern Number                                       | Refer to Application Note 1891 |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                      |                                |

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ) | 52°C/W                         |

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7. using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

#### **Electrical Characteristics**

$(THM = AGND, CEN = INT\_3V3, V_{BAT} = 4.2V, V_{BUS\_}, \overline{EXT\_PWRON, UOK}, \overline{IRQ}, \overline{CHG\_TYPE}, and \overline{CHG\_STAT} \ are \ unconnected, T_{AUS}, T_{AU$ = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                | SYMBOL           | CONDITIONS                                                         | MIN | TYP | MAX | UNITS |  |  |

|--------------------------|------------------|--------------------------------------------------------------------|-----|-----|-----|-------|--|--|

| USB-TO-SYS PREREGULATOR  |                  |                                                                    |     |     |     |       |  |  |

| USB Operating Range      | V <sub>BUS</sub> | Initial V <sub>BUS</sub> voltage before enabling charger           | 4.0 |     | 6.6 | V     |  |  |

| USB Standoff Voltage     |                  | V <sub>BAT</sub> = V <sub>SYS</sub> = 0V, I <sub>BUS</sub> < 800μA |     |     | 14  | V     |  |  |

| USB_OK Debounce<br>Timer | tusb_db          | Time from BUS within valid range until UOK goes high impedance     |     | 30  | 50  | ms    |  |  |

Maxim Integrated | 6 www.maximintegrated.com

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

## **Electrical Characteristics (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT}$ \_PWRON,  $\overline{IRQ}$ ,  $\overline{CHG}$ \_TYPE, and  $\overline{CHG}$ \_STAT are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                                  | SYMBOL                 | COND                                                            | ITIONS                                                            | MIN                        | TYP                        | MAX                        | UNITS |

|------------------------------------------------------------|------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

|                                                            |                        | UOK logic-low,<br>V <sub>BUS</sub> rising,<br>100mV hysteresis  | Before initial detection of external device                       | 3.85                       | 4.0                        | 4.15                       |       |

| USB Undervoltage<br>Lockout Threshold                      |                        | UOK logic-low,<br>V <sub>BUS</sub> falling,<br>customer UVLO    | For > 500mA<br>adapter and except<br>for ILIM [2:0] = 000,<br>111 | 3.40                       | 3.55                       | 3.70                       | V     |

|                                                            |                        | UOK logic-low,                                                  | USB 2.0 low-power device                                          | 3.75                       | 3.9                        | 4.05                       |       |

|                                                            |                        | V <sub>BUS</sub> falling                                        | USB 2.0 high-<br>power device                                     | 3.95                       | 4.1                        | 4.25                       |       |

| USB Overvoltage<br>Protection Threshold                    |                        | UOK logic-low, V <sub>BUS</sub> hysteresis                      | s rising, 100mV                                                   | 6.7                        | 6.9                        | 7.1                        | V     |

|                                                            | I <sub>DETECT</sub>    | Charge type detection<br>0mA                                    | on, I <sub>SYS</sub> = I <sub>BAT</sub> =                         |                            |                            | 0.5                        |       |

| USB Input Supply<br>Current (Notes 3, 4)                   | I <sub>ENUMERATE</sub> | USB 2.0 enumeration I <sub>BAT</sub> = 0mA                      | n in progress, I <sub>SYS</sub> =                                 |                            |                            | 100                        |       |

|                                                            | I <sub>SUSPEND</sub>   | Suspended mode, I <sub>S</sub><br>V <sub>STDB_EN_HW</sub> = 0V  | <sub>SYS</sub> = I <sub>BAT</sub> = 0mA,                          |                            |                            | 0.5                        | mA    |

|                                                            |                        | USB 2.0 low-power device detected                               | $T_A = 0^{\circ}C \text{ to } +85^{\circ}C$                       |                            |                            | 100                        |       |

|                                                            |                        |                                                                 | T <sub>A</sub> = -40°C to<br>+85°C                                |                            |                            | 102.5                      |       |

|                                                            | IUSB_500mA             |                                                                 | USB 2.0 high-<br>power device<br>detected                         |                            |                            | 500                        |       |

|                                                            | I <sub>SUS</sub>       | USB 2.0 low-power device detected                               | During suspend                                                    |                            | 0                          |                            |       |

|                                                            | I <sub>ENU</sub>       | During USB enumera                                              | ation, T <sub>A</sub> = +25°C                                     | 80                         | 90                         | 98                         |       |

|                                                            | I <sub>USB_LP</sub>    | USB 2.0 low-power of +25°C                                      | device detected, T <sub>A</sub> =                                 | 80                         | 90                         | 98                         | 1     |

|                                                            | I <sub>USB_HP</sub>    | USB 2.0 high-power                                              | device detected                                                   | 455                        | 475                        | 490                        |       |

|                                                            |                        | I <sub>LIM</sub> = 000, T <sub>A</sub> = +25                    | °C                                                                | 80                         | 90                         | 98                         |       |

| USB Input Current Limit                                    |                        | ILIM = 001 (default)                                            |                                                                   | 455                        | 475                        | 490                        | mA    |

|                                                            |                        | ILIM = 010                                                      |                                                                   |                            | 600                        |                            |       |

|                                                            |                        | ILIM = 011                                                      |                                                                   |                            | 700                        |                            |       |

|                                                            | I <sub>LIMIT</sub>     | ILIM = 100                                                      |                                                                   |                            | 900                        |                            |       |

|                                                            |                        | ILIM = 101                                                      |                                                                   |                            | 1000                       |                            | 1     |

|                                                            |                        | ILIM = 110, T <sub>A</sub> = +25                                | 5°C (Note 3)                                                      | 1344                       | 1500                       | 1650                       | 1     |

|                                                            |                        | ILIM = 110, T <sub>A</sub> = -40°C to +85°C                     |                                                                   | 1324                       | 1500                       | 1700                       | 1     |

| V <sub>BUS</sub> _ to V <sub>SYS</sub> _ On-<br>Resistance |                        | V <sub>BUS</sub> = 5V, I <sub>SYS</sub> = 400mA                 |                                                                   |                            | 200                        | 320                        | ml    |

| V <sub>SYS</sub> to V <sub>BAT</sub> _Reverse Regulation   |                        | When SYS is in regulators, V <sub>SYS</sub> falling, hysteresis |                                                                   | V <sub>BAT</sub> -<br>80mV | V <sub>BAT</sub> -<br>50mV | V <sub>BAT</sub> -<br>20mV |       |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

## **Electrical Characteristics (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT}$ \_PWRON,  $\overline{IRQ}$ ,  $\overline{CHG}$ \_TYPE, and  $\overline{CHG}$ \_STAT are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                             | SYMBOL                  | COND                                                  | CONDITIONS                                           |                                | TYP                         | MAX                         | UNITS |

|---------------------------------------|-------------------------|-------------------------------------------------------|------------------------------------------------------|--------------------------------|-----------------------------|-----------------------------|-------|

| Input Limiter Soft-Start Time         |                         | Input current ramp ti                                 |                                                      | 50                             | 100                         | μs                          |       |

|                                       |                         | THERM_REG = 00                                        |                                                      |                                | 90                          |                             |       |

| Thermal-Limit Start                   | _                       | THERM _REG = 01                                       |                                                      |                                | 100                         |                             | °C    |

| Temperature                           | T <sub>DIE_LIM</sub>    | THERM _REG = 10                                       |                                                      |                                | 110                         |                             | ٠.    |

|                                       |                         | THERM _REG = 11                                       |                                                      |                                | 120                         |                             |       |

| Thermal-Limit Triggers IRQ            |                         |                                                       |                                                      | T <sub>DIE_LIM</sub><br>+ 10°C |                             | °C                          |       |

| Thermal-Limit Gain                    |                         | I <sub>SYS</sub> reduction/die te                     |                                                      | 5                              |                             | %/°C                        |       |

| SYS Regulation Voltage                |                         | V <sub>BAT</sub> > 3.45V, I <sub>SYS</sub>            | = 1mA to 1.6A                                        |                                | 140mV +<br>V <sub>BAT</sub> | 210mV +<br>V <sub>BAT</sub> | V     |

|                                       |                         |                                                       | V_SYS = 00                                           |                                | 3.4                         |                             |       |

| Minimum SYS<br>Regulation Voltage     |                         |                                                       | V_SYS = 01 T <sub>A</sub> = +25°C                    | 4.2                            | 4.35                        | 4.524                       |       |

|                                       | V <sub>SYS_MIN</sub>    | V <sub>BUS</sub> = 6V, I <sub>SYS</sub> = 1mA to 1.6A | V_SYS = 02 T <sub>A</sub> = -40°C to +85°C           | 4.185                          | 4.35                        | 4.524                       | V     |

|                                       |                         |                                                       | V_SYS = 10                                           |                                | 4.4                         |                             |       |

|                                       |                         |                                                       | V_SYS = 11                                           |                                | 4.5                         |                             |       |

| Under olter of Lealer. A              | .,                      | V <sub>BUS</sub> = 5.5V rising                        | V <sub>BUS</sub> _ = 5.5V rising                     |                                | 3.0                         |                             |       |

| Undervoltage Lockout                  | V <sub>SYS_UVLO</sub>   | V <sub>BUS</sub> _ = 5.5V falling                     | V <sub>BUS</sub> = 5.5V falling                      |                                | 2.85                        | 3.1                         | V     |

| CHARGER                               |                         |                                                       |                                                      |                                |                             |                             |       |

| BAT-to-SYS On-<br>Resistance          |                         | V <sub>BAT</sub> = 4.2V, I <sub>SYS</sub> =           | : 200mA                                              |                                | 55                          | 80                          | ml    |

|                                       | V <sub>BAT_UVLO_F</sub> | V <sub>BAT</sub> falling                              | BAT_UVLO_VPRE<br>Q = 1 (register<br>0x10h)           | 2.15                           | 2.40                        | 2.65                        | V     |

| BAT Undervoltage<br>Lockout (Register | V <sub>BAT_UVLO_R</sub> | V <sub>BAT</sub> rising                               | BAT_UVLO_VPRE<br>Q = 1 (register<br>0x10h)           | 2.45                           | 2.70                        | 2.95                        |       |

| 0x10h, Bit 7 = 0)                     | V <sub>BAT_UVLO_F</sub> | V <sub>BAT</sub> falling                              | BAT_UVLO_VPRE<br>Q = 0 (default,<br>register 0x10h)  | 1.60                           | 1.85                        | 2.10                        |       |

|                                       | V <sub>BAT_UVLO_R</sub> | V <sub>BAT</sub> rising                               | BAT_UVLO_VPRE<br>Q = 0 (default,<br>register 0x10h)  | 1.85                           | 2.10                        | 2.35                        |       |

| Charger Soft-Start Time               |                         |                                                       |                                                      |                                | 1                           |                             | ms    |

| PAT Lookaga Current                   | V <sub>BAT</sub> = 4.2  | V- · 4 2V                                             | V <sub>BUS</sub> not connected                       |                                | 2                           | 6                           | ^     |

| BAT Leakage Current                   |                         | VBAT = 4.2V                                           | V <sub>BUS</sub> connected,<br>V <sub>CEN</sub> = 0V |                                | 6                           | 15                          | μA    |

| PRECHARGE MODE                        |                         |                                                       |                                                      |                                |                             |                             |       |

| BAT Precharge Current                 | I <sub>PCHG</sub>       | V <sub>BAT</sub> > 1.4V (Note 5                       | 5)                                                   |                                | 50                          |                             | mA    |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

## **Electrical Characteristics (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT}$ \_PWRON, UOK,  $\overline{IRQ}$ ,  $\overline{CHG}$ \_TYPE, and  $\overline{CHG}$ \_STAT are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                         | SYMBOL                      | COND                                                                                                                                                           | ITIONS                                              | MIN  | TYP                        | MAX  | UNITS |  |

|-----------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|----------------------------|------|-------|--|

|                                   | V <sub>BAT_PCHG_F</sub>     | V <sub>BAT</sub> falling                                                                                                                                       | BAT_UVLO_VPRE<br>Q = 1 (register<br>0x10h)          | 2.60 | 2.70                       | 2.80 |       |  |

| BAT Prequalification<br>Threshold | V <sub>BAT_PCHG_R</sub>     | V <sub>BAT</sub> rising                                                                                                                                        | BAT_UVLO_VPRE<br>Q = 1 (register<br>0x10h)          | 2.70 | 2.80                       | 2.95 | V     |  |

|                                   | V <sub>BAT_PCHG_F</sub>     | V <sub>BAT</sub> falling                                                                                                                                       | BAT_UVLO_VPRE<br>Q = 0 (default,<br>register 0x10h) | 2.05 | 2.15                       | 2.25 |       |  |

|                                   | V <sub>BAT_PCHG_R</sub>     | V <sub>BAT</sub> rising                                                                                                                                        | BAT_UVLO_VPRE<br>Q = 0 (default,<br>register 0x10h) | 2.15 | 2.25                       | 2.40 |       |  |

| FAST-CHARGE MODE                  |                             |                                                                                                                                                                |                                                     |      |                            |      |       |  |

|                                   |                             | I <sub>FCHG</sub> = 000                                                                                                                                        |                                                     |      | 100                        |      |       |  |

| BAT Charge-Current Set<br>Range   |                             | I <sub>FCHG</sub> = 010 (default                                                                                                                               | )                                                   |      | 200                        |      |       |  |

|                                   | Іғснд                       | I <sub>FCHG</sub> = 001                                                                                                                                        |                                                     |      | 300                        |      |       |  |

|                                   |                             | I <sub>FCHG</sub> = 110                                                                                                                                        |                                                     |      | 370                        |      | mA    |  |

|                                   |                             | I <sub>FCHG</sub> = 111                                                                                                                                        |                                                     |      | 450                        |      |       |  |

|                                   |                             | I <sub>FCHG</sub> = 011                                                                                                                                        |                                                     |      | 600                        | _    |       |  |

|                                   |                             | I <sub>FCHG</sub> = 100                                                                                                                                        |                                                     | 800  |                            |      |       |  |

|                                   |                             | I <sub>FCHG</sub> = 101                                                                                                                                        |                                                     |      | 900                        |      |       |  |

|                                   | VBAT_FCHG_R  VBAT_FCHG_H YS | V <sub>BAT</sub> rising threshold, where charging current I <sub>FCHG</sub> is reduced to I <sub>TCHG</sub> V <sub>BAT</sub> hysteresis, the falling threshold | BAT_FCHG = 00                                       |      | 3.8                        |      |       |  |

|                                   |                             |                                                                                                                                                                | BAT_FCHG = 01                                       |      | 3.9                        |      | V     |  |

|                                   |                             |                                                                                                                                                                | BAT_FCHG = 10<br>(default)                          | 3.88 | 4                          | 4.12 |       |  |

|                                   |                             |                                                                                                                                                                | BAT_FCHG = 11                                       |      | 4.1                        |      |       |  |

| BAT Fast-Charge<br>Threshold      |                             |                                                                                                                                                                | BAT_FCHG_HYS<br>= 00                                |      | 150                        |      | - mV  |  |

|                                   |                             | where charging current is increased                                                                                                                            | BAT_FCHG_HYS<br>= 01 (default)                      |      | 200                        |      |       |  |

|                                   |                             | to I <sub>FCHG</sub> is:<br>VBAT_FCHG_HYS =                                                                                                                    | BAT_FCHG_HYS<br>= 10                                |      | 250                        |      |       |  |

|                                   |                             | VBAT_FCHG_R -<br>VBAT_FCHG_F                                                                                                                                   | BAT_FCHG_HYS<br>= 11                                |      | 300                        |      | 1     |  |

| TOP-OFF CHARGE MOD                | E                           |                                                                                                                                                                |                                                     |      |                            |      |       |  |

|                                   |                             |                                                                                                                                                                | TCHG = 00                                           |      | 0.4 x                      |      |       |  |

|                                   |                             |                                                                                                                                                                | -                                                   |      | I <sub>FCHG</sub>          |      | _     |  |

|                                   |                             | V <sub>BAT</sub> > 1.4V                                                                                                                                        | TCHG = 01                                           |      | 0.6 x<br>I <sub>FCHG</sub> |      |       |  |

| Top-Off Charge Current            | ITCHG                       | (Note 5)                                                                                                                                                       | TOUG 45                                             |      | 0.8 x                      |      | mA    |  |

|                                   |                             | (Note 5)                                                                                                                                                       | TCHG = 10                                           |      | I <sub>FCHG</sub>          |      |       |  |

|                                   |                             |                                                                                                                                                                | TCHG = 11                                           |      | 1.0 x                      |      | 7     |  |

|                                   |                             |                                                                                                                                                                | (default)                                           |      | I <sub>FCHG</sub>          |      |       |  |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

## **Electrical Characteristics (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT}$ \_PWRON,  $\overline{UOK}$ ,  $\overline{IRQ}$ ,  $\overline{CHG}$ \_TYPE, and  $\overline{CHG}$ \_STAT are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                          | SYMBOL                 | CONDITIONS                       |                                                            | MIN   | TYP   | MAX   | UNITS   |  |

|------------------------------------|------------------------|----------------------------------|------------------------------------------------------------|-------|-------|-------|---------|--|

|                                    |                        | CHG_DONE = 000                   |                                                            | 10    |       |       |         |  |

|                                    |                        | CHG_DONE = 001                   |                                                            | 20    |       |       |         |  |

|                                    |                        | CHG_DONE = 010                   |                                                            | 30    | 40    | 50    |         |  |

| Charge DONE                        |                        | CHG_DONE = 011                   |                                                            | 37.5  | 50    | 62.5  |         |  |

| Qualification (Note 3)             | ICHG_DONE              | CHG_DONE = 100 (                 | default)                                                   | 45    | 60    | 75    | - mA    |  |

|                                    |                        | CHG_DONE = 101                   |                                                            |       | 80    |       |         |  |

|                                    |                        | CHG_DONE = 110                   |                                                            |       | 100   |       |         |  |

|                                    |                        | CHG_DONE = 111                   |                                                            |       | 120   |       | 1       |  |

|                                    |                        | _                                | BAT_REG = 00                                               |       | 4.05  |       |         |  |

|                                    |                        |                                  | BAT_REG = 01                                               |       | 4.10  |       |         |  |

|                                    |                        |                                  | BAT_REG = 10                                               |       | 4.15  |       |         |  |

| BAT Regulation Voltage (MAX77301)  | V <sub>BAT_REG</sub>   | I <sub>BAT</sub> _ = 0mA         | BAT_REG = 11<br>(default)<br>T <sub>A</sub> = +25°C        | 4.179 | 4.200 | 4.221 | V       |  |

|                                    |                        |                                  | BAT_REG = 11<br>(default)<br>T <sub>A</sub> = 0°C to +85°C | 4.158 | 4.200 | 4.242 |         |  |

|                                    | V <sub>BAT_REG</sub>   | I <sub>BAT</sub> _ = 0mA         | BAT_REG = 00                                               |       | 4.25  |       | V       |  |

|                                    |                        |                                  | BAT_REG = 01                                               |       | 4.30  |       |         |  |

|                                    |                        |                                  | BAT_REG = 10                                               |       | 4.35  |       |         |  |

| BAT Regulation Voltage (MAX77301A) |                        |                                  | BAT_REG = 11<br>(default)<br>T <sub>A</sub> = +25°C        | 4.378 | 4.40  | 4.422 |         |  |

|                                    |                        |                                  | BAT_REG = 11<br>(default)<br>T <sub>A</sub> = 0°C to +85°C | 4.356 | 4.40  | 4.444 |         |  |

|                                    |                        |                                  | BAT_RECHG = 00 (default)                                   |       | -350  |       |         |  |

| BAT Recharge                       | V <sub>BAT_RECHG</sub> | With respect to                  | BAT_RECHG = 10                                             |       | -300  |       | mV      |  |

| Threshold                          | B/(1_1(20110           | V <sub>BAT_REG</sub>             | BAT_RECHG = 01                                             |       | -250  |       | -       |  |

|                                    |                        |                                  | BAT_RECHG = 11                                             |       | -200  |       |         |  |

| CHARGE TIMER                       |                        |                                  |                                                            |       |       |       |         |  |

|                                    |                        | From start of                    | PCHG_TMR = 00                                              |       | 30    |       |         |  |

|                                    |                        | precharge until end              | PCHG_TMR = 01                                              |       | 60    |       |         |  |

| Prequalification Timer             | t <sub>PCHG</sub>      | of prequalification charge model | PCHG_TMR = 10<br>(default)                                 |       | 120   |       | Minutes |  |

|                                    |                        | ( <u>Figure 11</u> )             | PCHG_TMR = 11                                              |       | 240   |       |         |  |

|                                    |                        |                                  | FCHG_TMR = 00                                              |       | 75    |       |         |  |

|                                    |                        | From start of fast               | FCHG_TMR = 01                                              |       | 150   |       | Minutes |  |

| Fast-Charge Timer                  | t <sub>FCHG</sub>      | charge until maintains charge    | FCHG_TMR = 10                                              |       | 300   |       |         |  |

|                                    |                        | ( <u>Figure 11</u> )             | FCHG_TMR = 11<br>(default)                                 |       | 600   |       |         |  |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

## **Electrical Characteristics (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT}$ \_PWRON,  $\overline{UOK}$ ,  $\overline{IRQ}$ ,  $\overline{CHG}$ \_TYPE, and  $\overline{CHG}$ \_STAT are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                | SYMBOL                | CONI                                                                                    | MIN                                                    | TYP   | MAX   | UNITS |         |

|------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|---------|

|                                          |                       |                                                                                         | MTCHG_TMR = 10 (default)                               |       | 0     |       |         |

| Maintain-Charge Timer                    | <sup>t</sup> мтснg    | (Figure 12)                                                                             | MTCHG_TMR = 01                                         |       | 15    |       | Minutes |

| -                                        |                       |                                                                                         | MTCHG_TMR = 00                                         |       | 30    |       |         |

|                                          |                       |                                                                                         | MTCHG_TMR = 11                                         |       | 60    |       |         |

| Timer Accuracy                           |                       |                                                                                         |                                                        | -30   |       | +30   | %       |

| Timer Extend Threshold                   |                       | Percentage of charge which timer clock of                                               | ge current below<br>perates at half speed              | 50    |       |       | %       |

| Timer Suspend<br>Threshold               |                       | Percentage of charge which timer clock pa                                               |                                                        | 20    |       |       | %       |

| INSERTION AND REMOV                      | AL DETECTION          | N                                                                                       |                                                        |       |       |       |         |

| BAT Discharge Current                    | I <sub>DIS</sub>      | $1V \le V_{BAT} \le 4.2V$                                                               | C <sub>BAT</sub> ≤ 10μF                                | 0.375 |       | 1.125 | mA      |

| BAT Discharge Time                       | t <sub>DIS</sub>      | Discharge timer exp<br>V <sub>BAT_UVLO</sub> threshound<br>10µF                         | oires if V <sub>BAT</sub> drop ><br>old, battery cap ≤ |       | 150   |       | ms      |

| Charge Debounce Timer                    | t <sub>DB</sub>       | Delay before check                                                                      | ing charge done                                        | 100   | 150   | 200   | ms      |

| Battery Detecting<br>Current             | I <sub>BAT_DET</sub>  | Charging in progras<br>charge or maintain<br>if I <sub>BAT</sub> < I <sub>BAT_DET</sub> | charge);                                               | 1     | 3     | 5     | mA      |

| ADAPTER TYPE DETEC                       | TION                  |                                                                                         |                                                        |       |       |       |         |

| D- Current Sink                          | I <sub>DM_SINK</sub>  |                                                                                         |                                                        | 50    | 100   | 150   | μA      |

| D+ Current source                        | I <sub>DP_SRC</sub>   |                                                                                         |                                                        | 7     |       | 13    | μA      |

| D- Weak Current Sink                     | I <sub>DM_CD_PD</sub> |                                                                                         |                                                        |       |       | 0.1   | μA      |

| D+ Source Voltage                        | V <sub>DP_SRC</sub>   | I <sub>DP_SRC</sub> = 200μA                                                             |                                                        | 0.5   | 0.6   | 0.7   | V       |

| D+ Detection Threshold                   | V <sub>DAT_REF</sub>  |                                                                                         |                                                        | 0.25  | 0.32  | 0.40  | V       |

| D- Logic-High Threshold                  | $V_{DM\_IH}$          |                                                                                         |                                                        | 8.0   |       | 2.0   | V       |

| D+ Logic-High<br>Threshold               | V <sub>DP_IH</sub>    |                                                                                         |                                                        | 0.8   |       | 2.0   | V       |

|                                          | DP_25%<br>DM_25%      | Detection threshold as % of V <sub>BUS</sub>                                            | for custom chargers                                    | 23.75 | 25.0  | 26.25 |         |

| D+/D- Detection                          | DM_34%                | Detection threshold as % of V <sub>BUS</sub>                                            | for custom chargers                                    | 32.3  | 34    | 35.7  | %       |

| Threshold                                | DP_47%<br>DM_47%      | Detection threshold as % of V <sub>BUS</sub>                                            | for custom chargers                                    | 44.65 | 47.00 | 49.4  | 70      |

|                                          | DP_60%<br>DM_60%      | Detection threshold as % of V <sub>BUS</sub>                                            | for custom chargers                                    | 57    | 60    | 63    |         |

| D- Pulldown Resistor                     | R <sub>DM_DWN</sub>   |                                                                                         |                                                        | 14.25 |       | 24.8  | kΩ      |

| D- Pullup Resistor                       | R <sub>DM_PU</sub>    | External resistor = 3                                                                   | 33Ω, low speed only                                    | 1.425 | 1.500 | 1.575 | kΩ      |

| D+ Pullup Resistor                       | R <sub>DP_PU</sub>    | External resistor = 3                                                                   | 33Ω, full speed only                                   | 1.425 | 1.500 | 1.575 | kΩ      |

| D+ Charger Detection<br>Pullup Resistor  | R <sub>DP_CD_PU</sub> | RDP_CD_PU conn                                                                          | ected to INT_3V3                                       | 200   | 330   | 600   | kΩ      |

| Data Contact Detection<br>Debounce Timer | tDCD_DBNC             |                                                                                         |                                                        |       | 30    |       | ms      |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

## **Electrical Characteristics (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT}$ \_PWRON,  $\overline{IRQ}$ ,  $\overline{CHG}$ \_TYPE, and  $\overline{CHG}$ \_STAT are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                              | SYMBOL                                            | CONE                                                                                | DITIONS                                                  | MIN                                 | TYP  | MAX                 | UNITS                        |  |  |  |

|----------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------|------|---------------------|------------------------------|--|--|--|

| D+ Source On Time                      | t <sub>DP_SRC_ON</sub>                            |                                                                                     |                                                          | 100                                 |      |                     | ms                           |  |  |  |

| D+ Source to High-<br>Current Time     | t <sub>DP_SRC_HC</sub>                            |                                                                                     |                                                          | 40                                  |      |                     | ms                           |  |  |  |

| Enumeration Time Limit                 | tENUM                                             | Time from start of el until enumeration                                             | Time from start of enumeration process until enumeration |                                     |      |                     |                              |  |  |  |

| Reenumeration Timer                    | tre_enum                                          | Time from suspend enumerates, RWU_                                                  | mode until it re-<br>EN = 1                              |                                     | 100  |                     | ms                           |  |  |  |

| Reconnect Timer                        | t <sub>FAULT</sub>                                |                                                                                     | umeration to adapter abled, nENU_EN = 0                  |                                     | 3    |                     | s                            |  |  |  |

| Detecting Time                         |                                                   | D+/D- open power s                                                                  | ource nENU_EN = 1                                        |                                     | 100  |                     | ms                           |  |  |  |

| Enumeration Fail to<br>Reconnect Timer | tenu_fault                                        | Time from enumerar until enumeration is time from enumeration reconnect timer is st | retried at 100mA or on fail at 100mA until               |                                     | 87   |                     | ms                           |  |  |  |

| XIN, XOUT PINS                         |                                                   |                                                                                     |                                                          |                                     |      |                     |                              |  |  |  |

| Oscillator Frequency<br>Accuracy       |                                                   | Internal oscillator (lo                                                             | w speed), T <sub>A</sub> =                               | 5.91                                | 6.00 | 6.09                | MHz                          |  |  |  |

| XIN, XOUT Input<br>Capacitance         |                                                   | With external crysta                                                                | (full speed)                                             |                                     | 3    |                     | pF                           |  |  |  |

| XIN Input Current                      |                                                   | With external crysta                                                                | l (full speed)                                           |                                     |      | 10                  | FA                           |  |  |  |

| XIN Logic-High Input<br>Voltage        |                                                   |                                                                                     |                                                          | 0.667 x<br>V <sub>INT_3V</sub><br>3 |      | V <sub>INT_3V</sub> | V                            |  |  |  |

| XIN Logic-Low Input<br>Voltage         |                                                   |                                                                                     |                                                          |                                     |      | 0.4                 | ٧                            |  |  |  |

| THERMISTOR MONITOR                     | R (THM)                                           |                                                                                     |                                                          | •                                   |      |                     | •                            |  |  |  |

| THM Hot Threshold                      | T <sub>4</sub>                                    | V <sub>THM</sub> raising, 2% h                                                      | ysteresis                                                |                                     | 32.2 |                     | % of V <sub>INT_3V3</sub>    |  |  |  |

| THM Warm Threshold                     | Т3                                                | V <sub>THM</sub> raising, 2% h                                                      | ysteresis                                                |                                     | 46.5 |                     | % of<br>V <sub>INT_3V3</sub> |  |  |  |

| THM Cool Threshold                     | T <sub>2</sub>                                    | V <sub>THM</sub> falling, 2% hy                                                     | steresis                                                 |                                     | 81.9 |                     | % of<br>V <sub>INT_3V3</sub> |  |  |  |

| THM Cold Threshold                     | T <sub>1</sub>                                    | V <sub>THM</sub> falling, 2% hy                                                     | steresis                                                 |                                     | 88.7 |                     | % of V <sub>INT_3V3</sub>    |  |  |  |

| THM Disable Threshold                  |                                                   | V <sub>THM</sub> falling, 2% hy                                                     | steresis                                                 |                                     | 3.4  |                     | % of V <sub>INT_3V3</sub>    |  |  |  |

| THM Input Impedance                    | THM <sub>ZIN</sub>                                | High impedance wh disabled                                                          | en no BUS or THM is                                      |                                     | 500  |                     | kΩ                           |  |  |  |

|                                        |                                                   | THM = AGND<br>THERM_EN = 0                                                          | -1                                                       | 0.001                               | +1   | 11.4                |                              |  |  |  |

| THM Input Leakage                      | THM = AGND<br>THERM_EN = 1 T <sub>A</sub> = +85°C |                                                                                     |                                                          |                                     |      |                     | μA                           |  |  |  |

| EXT_PWRON                              |                                                   |                                                                                     |                                                          |                                     |      |                     |                              |  |  |  |

| Logic-Low Output<br>Voltage            |                                                   | Sinking 10mA                                                                        |                                                          |                                     | 35   | 100                 | mV                           |  |  |  |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

## **Electrical Characteristics (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT}$ \_PWRON,  $\overline{IRQ}$ ,  $\overline{CHG}$ \_TYPE, and  $\overline{CHG}$ \_STAT are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                           | SYMBOL                    | COND                                                  | ITIONS                              | MIN | TYP   | MAX | UNITS |

|-----------------------------------------------------|---------------------------|-------------------------------------------------------|-------------------------------------|-----|-------|-----|-------|

| High-Impedance Time                                 | text_pwr_re<br>SET        | Time where EXT_P\ impedance during tr EXT_PWRON low s | ansition between two                |     | 63    |     | ms    |

| CHARGER STATUS (CH                                  | G_STAT)                   |                                                       |                                     |     |       |     |       |

| Logic-Low Output<br>Voltage                         |                           | Sinking 10mA                                          |                                     |     | 35    | 100 | mV    |

| Blink Period for<br>Temperature Suspend<br>Mode     |                           | 50% duty cycle, batt                                  | ery present                         |     | 1.5   |     | s     |

| Blink Period for Timeout Mode                       |                           | 50% duty cycle, batt                                  | ery present                         |     | 0.15  |     | s     |

| LOGIC I/O: UOK, CEN, E                              | NU_EN_HW                  |                                                       |                                     |     |       |     |       |

|                                                     |                           | High level                                            |                                     | 1.3 |       |     |       |

| Logic Input Voltage                                 |                           | High level for SDA a                                  | nd SCL                              | 1.4 |       |     | V     |

|                                                     |                           | Low level                                             |                                     |     |       | 0.4 |       |

| Logic Input-Leakage                                 |                           | 2/ 22/1 5 51/                                         | T <sub>A</sub> = +25°C              |     | 0.001 | 1   |       |

| Current                                             |                           | $V_{BUS} = 0V \text{ to } 5.5V$                       | T <sub>A</sub> = +85°C              |     | 0.01  |     | μA    |

| Logic-Low Output Voltage (CHG_TYPE, IRQ, UOK, Only) |                           | Sinking 10mA                                          |                                     | 35  | 100   | mV  |       |

| Logic-High Output-                                  |                           |                                                       | T <sub>A</sub> = +25°C              |     | 0.001 | 1   |       |

| Leakage Current<br>(CHG_TYPE, IRQ,<br>UOK, Only)    |                           | V <sub>SYS</sub> = 5.5V                               | T <sub>A</sub> = +85°C              |     | 0.01  |     | μA    |

| UOK Blink Period<br>During USB Suspend              |                           | Only for USB autom suspend mode, 50%                  |                                     |     | 1.5   |     | s     |

| UOK Blink Period with Open D+/D- Detected           |                           | 50% duty cycle                                        |                                     |     | 0.15  |     | s     |

| I <sup>2</sup> C INTERFACE (See Fig                 | <u>gure 20</u> ) (Note 3) | ·                                                     |                                     |     |       |     |       |

| Clock Frequency                                     |                           |                                                       |                                     |     |       | 400 | kHz   |

| Bus-Free Time Between START and STOP                | t <sub>BUF</sub>          |                                                       |                                     | 1.3 |       |     | μs    |

| Hold Time Repeated START Condition                  |                           |                                                       |                                     | 0.6 |       |     | μs    |

| SCL Low Period                                      | t <sub>LOW</sub>          |                                                       |                                     | 1.3 |       |     | μs    |

| SCL High Period                                     | tHIGH                     |                                                       |                                     | 0.6 |       |     | μs    |

| Setup Time Repeated START Condition                 | <sup>t</sup> SU_STA       |                                                       |                                     | 0.6 |       |     | μs    |

| SDA Hold Time                                       | thd_dat                   |                                                       |                                     | 0   |       |     | μs    |

| SDA Setup Time                                      | t <sub>SU_DAT</sub>       |                                                       |                                     | 100 |       |     | μs    |

| Maximum Suppressed<br>Pulse Width                   |                           | Width of spikes that by the input filter of I signals | must be suppressed both SDA and SCL |     | 50    |     | ns    |

# JEITA-Compliant, Li+ Charger with Smart Power Selector, Automatic Detection, and USB Enumeration

#### **Electrical Characteristics (continued)**

(THM = AGND, CEN = INT\_3V3,  $V_{BAT}$  = 4.2V,  $V_{BUS}$ ,  $\overline{EXT}$ \_PWRON,  $\overline{IRQ}$ ,  $\overline{CHG}$ \_TYPE, and  $\overline{CHG}$ \_STAT are unconnected,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                    | SYMBOL                              | CONDITIONS                                                                                                                                      | MIN | TYP  | MAX | UNITS |  |  |

|----------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|--|--|

| Setup Time for STOP<br>Condition             | tsu_sto                             |                                                                                                                                                 | 0.6 |      |     | μs    |  |  |

| USB DATA INTERFACE                           |                                     |                                                                                                                                                 | •   |      |     |       |  |  |

| Differential-Receiver Input Sensitivity      | V <sub>D</sub> + - V <sub>D</sub> - |                                                                                                                                                 | 0.2 |      |     | V     |  |  |

| Differential-Receiver<br>Common-Mode Voltage |                                     |                                                                                                                                                 | 0.8 |      | 2.5 | V     |  |  |

| D+, D- Input Impedance                       |                                     |                                                                                                                                                 | 300 |      |     | kΩ    |  |  |

| D+, D- Output Low<br>Voltage                 | V <sub>OL</sub>                     | $R_{LOAD}$ = 1.5kΩ from $V_{D-}$ to 3.6V                                                                                                        |     |      | 0.3 | V     |  |  |

| D+, D- Output High<br>Voltage                | $V_{OH}$                            | $R_{LOAD}$ = 15kΩ from D+ and D- to AGND                                                                                                        | 2.8 |      | 3.6 | V     |  |  |

| Driver Output<br>Impedance                   |                                     | Excludes external resistor                                                                                                                      | 2   | 7    | 11  | I     |  |  |