# 2.5/3.3V ECL Triple D Flip-Flop with Set and Reset

### MC100ES6030

The MC100ES6030 is a triple master-slave D flip-flop with differential outputs. When the clock input is low, data enters the master latch and transfers to the slave during a positive transition on the clock input.

Each flip-flop has individual Reset inputs while the Set input is shared. The Set and Reset inputs are asynchronous and override the clock inputs.

### **Features**

- 1.2 GHz minimum toggle frequency

- · 450 ps typical propagation delay

- LVPECL operating range:  $V_{CC} = 2.375 \text{ V}$  to 3.8 V,  $V_{EE} = 0 \text{ V}$

- LVECL operating range:  $V_{CC} = 0 \text{ V}$ ,  $V_{EE} = -2.375 \text{ V}$  to -3.8 V

- 20-lead SOIC package

- Ambient temperature range -40°C to +85°C

### ORDERING INFORMATION

| Device          | Package |

|-----------------|---------|

| MC100ES6030DW   | SO-20   |

| MC100ES6030DWR2 | SO-20   |

#### Q1 Q1 $V_{CC}$ $V_{CC}$ $V_{CC}$ 12 18 17 16 14 Q Q Q Q Q S S S 1 5 10 2 6 8 9 S012 D0 CLK0 D1 CLK1 R1 D2 CLK2 R2

Figure 1. 20-Lead Pinout (Top View) and Logic Diagram

### PIN DESCRIPTION

| PIN                     | FUNCTION                      |

|-------------------------|-------------------------------|

| D0-D2                   | ECL Data Inputs               |

| R0-R2                   | ECL Reset Inputs              |

| CLK0-CLK2               | ECL Clock Inputs              |

| S012                    | ECL Common Set Input          |

| Q0-Q2, <del>Q0-Q2</del> | ECL Differential Data Outputs |

| V <sub>CC</sub>         | Positive Supply               |

| V <sub>EE</sub>         | Negative Supply               |

### **TRUTH TABLE**

| R | S | D | CLK | Q     | Q     |

|---|---|---|-----|-------|-------|

| L | L | L | Z   | L     | Н     |

| L | L | Н | Z   | Н     | L     |

| Н | L | Х | Х   | L     | Н     |

| L | Н | Х | Х   | Н     | L     |

| Н | Н | Х | X   | Undef | Undef |

Z = LOW to HIGH Transition

X = Don't Care

**Table 1. GENERAL SPECIFICATIONS**

| Charact                                                     | Value             |  |  |  |  |  |

|-------------------------------------------------------------|-------------------|--|--|--|--|--|

| Internal Input Pulldown Resistor                            | TBD               |  |  |  |  |  |

| Internal Input Pullup Resistor                              | TBD               |  |  |  |  |  |

| ESD Protection                                              | TBD<br>TBD<br>TBD |  |  |  |  |  |

| θ <sub>JA</sub> Thermal Resistance<br>(Junction-to-Ambient) | TBD<br>TBD        |  |  |  |  |  |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test      |                   |  |  |  |  |  |

Table 2. ABSOLUTE MAXIMUM RATINGS<sup>a</sup>

| Symbol              | Rating                      | Conditions                                           | Rating                                         | Units    |

|---------------------|-----------------------------|------------------------------------------------------|------------------------------------------------|----------|

| V <sub>SUPPLY</sub> | Power Supply Voltage        | Difference between V <sub>CC</sub> & V <sub>EE</sub> | 3.9                                            | V        |

| V <sub>IN</sub>     | Input Voltage               | $V_{CC}$ - $V_{EE} \le 3.6 \text{ V}$                | V <sub>CC</sub> + 0.3<br>V <sub>EE</sub> - 0.3 | V<br>V   |

| l <sub>out</sub>    | Output Current              | Continuous<br>Surge                                  | 50<br>100                                      | mA<br>mA |

| T <sub>A</sub>      | Operating Temperature Range |                                                      | -40 to +85                                     | °C       |

| T <sub>store</sub>  | Storage Temperature Range   |                                                      | -65 to +150                                    | °C       |

a Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated conditions is not implied.

**Table 3. DC CHARACTERISTICS** ( $V_{CC} = 0 \text{ V}, V_{EE} = -2.5 \text{ V} \pm 5\% \text{ or } -3.8 \text{ V to } -3.135 \text{ V}; V_{CC} = 2.5 \text{ V} \pm 5\% \text{ or } 3.135 \text{ V to } 3.8 \text{ V}, V_{EE} = 0 \text{ V}$

|                 |                                  | -40°C                 |                       |                       | 0°C to 85°C           |                       |                       |      |

|-----------------|----------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------|

| Symbol          | Characteristic                   | Min                   | Тур                   | Max                   | Min                   | Тур                   | Max                   | Unit |

| I <sub>EE</sub> | Power Supply Current             |                       | TBD                   |                       |                       | TBD                   |                       | mA   |

| V <sub>OH</sub> | Output HIGH Voltage <sup>a</sup> | V <sub>CC</sub> -1085 | V <sub>CC</sub> -1005 | V <sub>CC</sub> -880  | V <sub>CC</sub> -1025 | V <sub>CC</sub> -955  | V <sub>CC</sub> -880  | mV   |

| V <sub>OL</sub> | Output LOW Voltage <sup>a</sup>  | V <sub>CC</sub> -1830 | V <sub>CC</sub> -1695 | V <sub>CC</sub> -1555 | V <sub>CC</sub> -1810 | V <sub>CC</sub> -1705 | V <sub>CC</sub> -1620 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage               | V <sub>CC</sub> -1165 |                       | V <sub>CC</sub> -880  | V <sub>CC</sub> -1165 |                       | V <sub>CC</sub> -880  | mV   |

| V <sub>IL</sub> | Input LOW Voltage                | V <sub>CC</sub> -1810 |                       | V <sub>CC</sub> -1475 | V <sub>CC</sub> -1810 |                       | V <sub>CC</sub> -1475 | mV   |

| I <sub>IN</sub> | Input Current                    |                       |                       | ± 150                 |                       |                       | ±150                  | μV   |

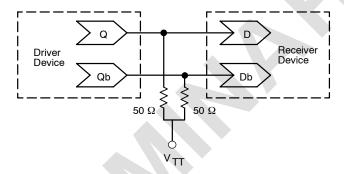

a Outputs are terminated through a  $50\Omega$  resistor to  $V_{CC}$ -2 volts. Output termination voltage  $V_{TT}$  = 0 V for  $V_{CC}$  = 2.5 V operation is supported, but the power consumption of the device will increase.

**Table 4. AC CHARACTERISTICS** ( $V_{CC} = 0 \text{ V}, V_{EE} = -2.5 \text{ V} \pm 5\% \text{ or } -3.8 \text{ V to } -3.135 \text{ V}; V_{CC} = 2.5 \text{ V} \pm 5\% \text{ or } 3.135 \text{ V to } 3.8 \text{ V}, V_{EE} = 0 \text{ V}$ )

|                                      |                              |             | -40°C      |          |     | 25°C       |          |     | 85°C       |          |     |          |

|--------------------------------------|------------------------------|-------------|------------|----------|-----|------------|----------|-----|------------|----------|-----|----------|

| Symbol                               | Characteristic               |             | Min        | Тур      | Max | Min        | Тур      | Max | Min        | Тур      | Max | Unit     |

| f <sub>max</sub>                     | Maximum Toggle Frequency     |             | 1.2        |          |     | 1.2        |          |     | 1.2        |          |     | GHz      |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay to Output  | CLK<br>S, R |            |          |     |            | 600      |     |            |          |     | ps       |

| t <sub>s</sub><br>t <sub>h</sub>     | Setup Time<br>Hold Time      |             | 150<br>200 | 0<br>100 |     | 150<br>200 | 0<br>100 |     | 150<br>200 | 0<br>100 |     | ps<br>ps |

| t <sub>RR</sub>                      | Set/Reset Recovery           |             | 200        | 100      |     | 200        | 100      |     | 200        | 100      |     | ps       |

| t <sub>PW</sub>                      | Minimum Pulse Width          | CLK<br>S, R | 400<br>650 |          |     | 400<br>650 |          |     | 400<br>650 |          |     | ps<br>ps |

| t <sub>JITTER</sub>                  | Cycle-to-Cylce Jitter        |             |            | < 2      |     |            | < 2      |     |            | < 2      |     | ps       |

| t <sub>r</sub> /t <sub>f</sub>       | Output Rise/Fall Time (20%-8 | 80%)        | TBD        | TBD      | TBD | TBD        | TBD      | TBD | TBD        | TBD      | TBD | ps       |

Figure 2. Typical Termination for Output Driver and Device Evaluation

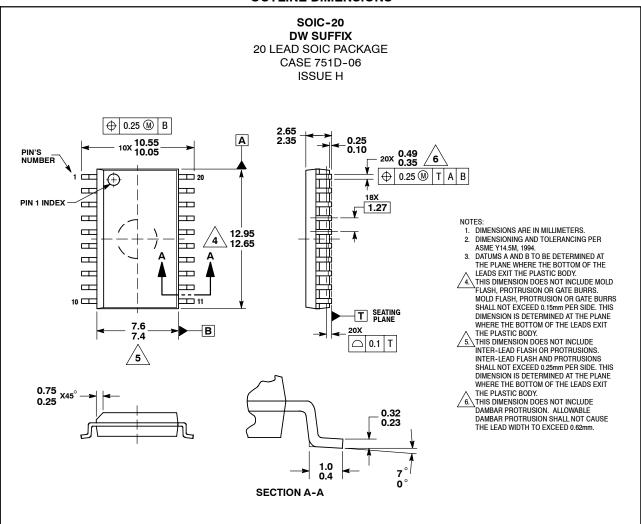

### **OUTLINE DIMENSIONS**

## Innovate with IDT and accelerate your future networks. Contact:

## www.IDT.com

### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

### **For Tech Support**

netcom@idt.com 480-763-2056

### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

### **Asia Pacific and Japan**

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339