# Si5345, Si5344, Si5342 Rev. D Family Reference Manual

Any-frequency, Any-output Jitter-Attenuators/Clock Multipliers Si5345, Si5344, Si5342 Family Reference Manual

This Family Reference Manual is intended to provide system, PCB design, signal integrity, and software engineers the necessary technical information to successfully use the Si5345/44/42 devices in end applications. The official device specifications can be found in the Si5345/44/42 data sheets.

#### RELATED DOCUMENTS

- Si5345/44/42 Rev D Data Sheet: https://www.skyworksinc.com/-/media/ Skyworks/SL/documents/public/datasheets/Si5345-44-42-D-DataSheet.pdf

- Si5345/44/42 Rev D Device Errata: https://www.skyworksinc.com/-/ media/Skyworks/SL/documents/public/ errata/Si5345-44-42-RevD-Errata.pdf

- Si5345 Rev D -EVB User Guide: https://www.skyworksinc.com/-/ media/Skyworks/SL/documents/public/ user-guides/Si5345-D-EVB.pdf

- Si5344 Rev D -EVB User Guide: https://www.skyworksinc.com/-/ media/Skyworks/SL/documents/public/ user-guides/Si5344-D-EVB.pdf

- Si5342 Rev D -EVB User Guide: https://www.skyworksinc.com/-/ media/Skyworks/SL/documents/public/ user-guides/Si5342-D-EVB.pdf

- Si534x/8x Jitter Attenuators Recommended Crystals, TCXO and OCXOs Reference Manual: https://www.skyworksinc.com/-/media/ Skyworks/SL/documents/public/referencemanuals/si534x-8x-9x-recommendedcrystals-rm.pdf

# **Table of Contents**

| 1. | Overview                                                           | . 5 |

|----|--------------------------------------------------------------------|-----|

| 2. | Work Flow Expectations with ClockBuilder Pro™ and the Register Map | . 6 |

|    | 2.1 Family Product Comparison                                      | . 7 |

|    | 2.2 Available Software Tools and Support                           | . 8 |

| 3. | DSPLL and MultiSynth                                               | . 9 |

|    | 3.1 Dividers                                                       |     |

|    | 3.2 DSPLL Loop Bandwidth                                           | .10 |

|    | 3.2.1 Fastlock Feature                                             |     |

|    | 3.2.2 Holdover Exit Bandwidth                                      |     |

| 4. | Modes of Operation                                                 |     |

|    | 4.1 Reset and Initialization                                       |     |

|    | 4.2 Dynamic PLL Changes                                            | .14 |

|    | 4.3 NVM Programming                                                |     |

|    | 4.4 Free Run Mode                                                  |     |

|    | 4.5 Acquisition Mode                                               |     |

|    | 4.6 Locked Mode                                                    |     |

|    | 4.7 Holdover Mode                                                  | .17 |

| 5. | Clock Inputs                                                       | 19  |

|    | 5.1 Inputs (IN0, IN1, IN2, IN3)                                    |     |

|    | 5.1.1 Manual Input Switching.                                      |     |

|    | 5.1.2 Automatic Input Selection                                    |     |

|    | 5.2 Types of Inputs                                                |     |

|    | 5.2.2 Hitless Input Switching with Phase Buildout                  |     |

|    | 5.2.3 Ramped Input Switching                                       |     |

|    | 5.2.4 Hitless Switching, LOL (loss of lock) and Fastlock           |     |

|    | 5.2.6 External Clock Switching                                     |     |

|    | 5.2.7 Synchronizing to Gapped Input Clocks                         |     |

|    | 5.2.8 Rise Time Considerations                                     |     |

|    | 5.3 Fault Monitoring                                               |     |

|    | 5.3.1 Input Loss of Signal (LOS) Fault Detection                   |     |

|    | 5.3.3 Loss of Lock (LOL) Fault Monitoring                          |     |

|    | 5.4 Interrupt (INTR) Monitoring                                    | .31 |

| 6. | Output Clocks                                                      | 32  |

|    | 6.1 Output Crosspoint Switch                                       |     |

|    | 6.2 Performance Guidelines for Outputs                             |     |

|    | 6.3 Output Signal Format                                              |     |

|----|-----------------------------------------------------------------------|-----|

|    | 6.3.1 Differential Output Terminations                                |     |

|    | 6.3.2 Differential Output Swing Modes                                 |     |

|    | 6.3.3 Programmable Common Mode Voltage for Differential Outputs       |     |

|    | 6.3.4 LVCMOS Output Terminations                                      |     |

|    | 6.3.5 LVCMOS Output Impedance and Drive Strength Selection            |     |

|    | 6.3.6 LVCMOS Output Signal Swing                                      |     |

|    | 6.3.7 LVCMOS Output Polarity                                          |     |

|    | 6.3.8 Output Driver Settings for LVPECL, LVDS, HCSL, and CML          |     |

|    | 6.4 Output Enable/Disable                                             |     |

|    | 6.4.1 Output Driver State When Disabled                               |     |

|    | 6.4.2 Synchronous Output Disable Feature                              |     |

|    | 6.5 Output Buffer Supply Voltage Selection                            |     |

| 7. | . Zero Delay Mode                                                     | 44  |

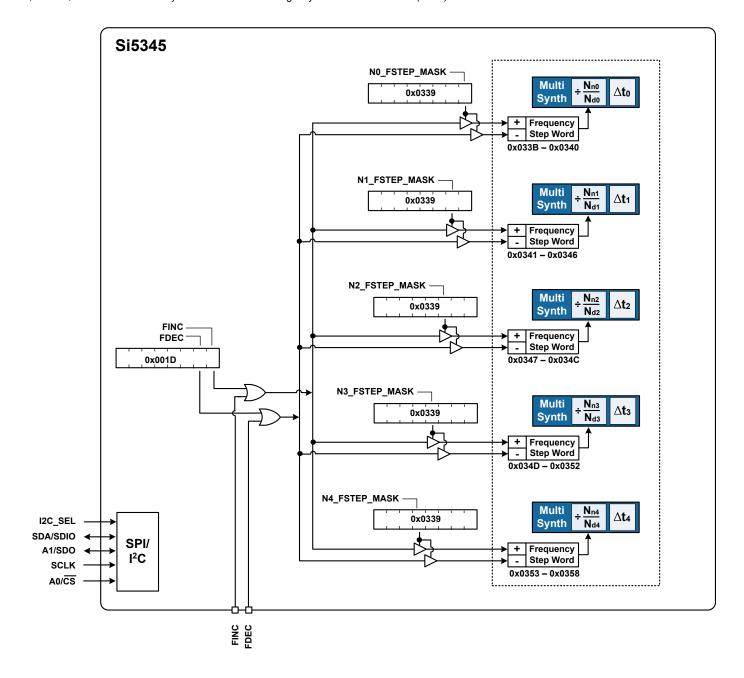

| 8. | . Digitally-Controlled Oscillator (DCO) Mode ........................ | 46  |

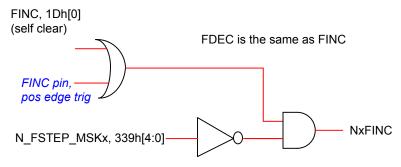

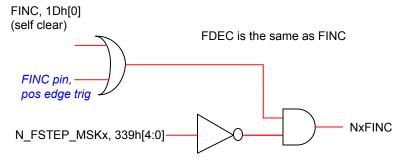

|    | 8.1 DCO with Frequency Increment/Decrement Pins/Bits                  | .47 |

|    | 8.2 DCO with Direct Register Writes                                   | .49 |

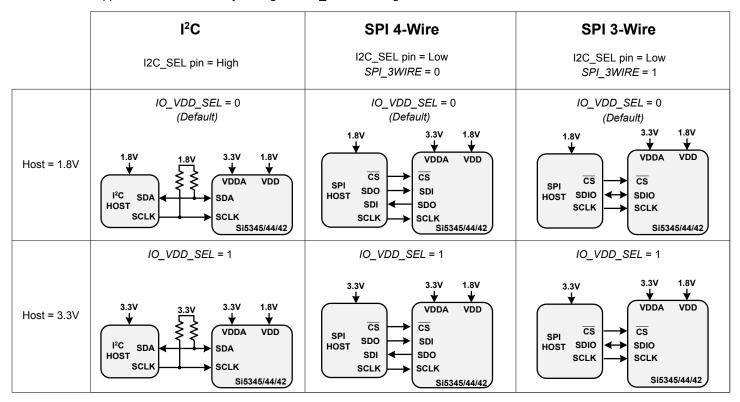

| 9. | . Serial interface                                                    | 50  |

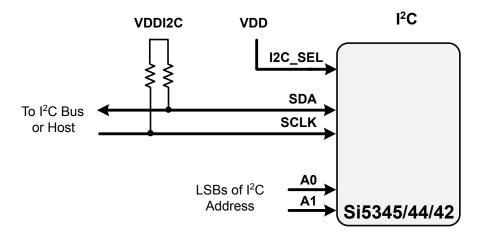

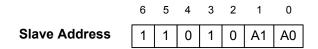

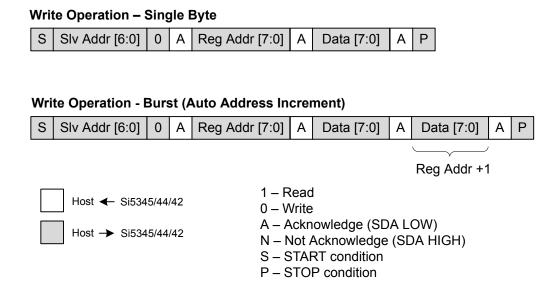

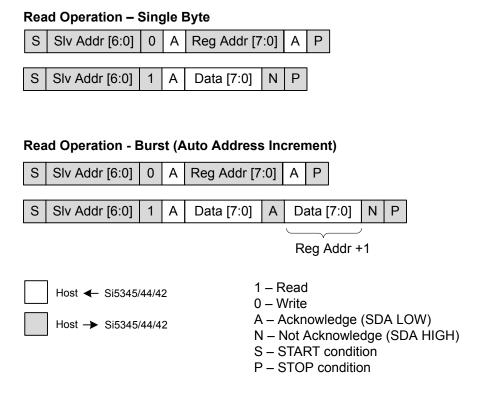

|    | 9.1 I <sup>2</sup> C Interface                                        | .51 |

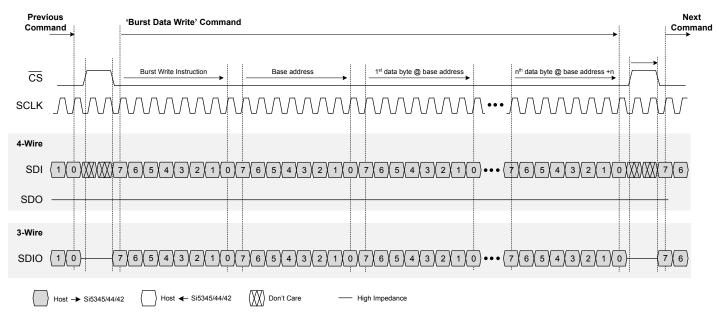

|    | 9.2 SPI Interface                                                     | .53 |

| 1( | 0. Field Programming. .............................                   | 58  |

| 11 | 1. XA/XB External References                                          | 59  |

|    | 11.1 Performance of External References                               | .59 |

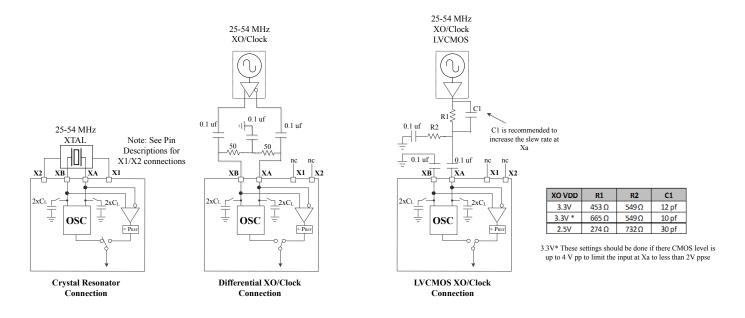

|    | 11.2 Recommended Crystals and External Oscillators                    | .60 |

|    | 11.3 Register Settings to Control External XTAL Reference             | .60 |

|    | 11.3.1 XAXB_EXTCLK_EN Reference Clock Selection Register              | .61 |

|    | 11.3.2 PXAXB Pre-scale Divide Ratio for Reference Clock Register      | .61 |

| 12 | 2. Crystal and Device Circuit Layout Recommendations                  | 62  |

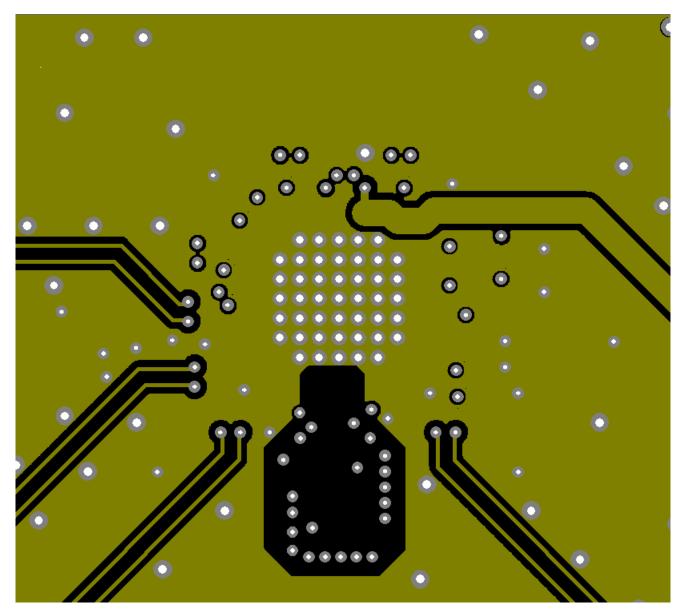

|    | 12.1 64-Pin QFN Si5345 Layout Recommendations                         | .62 |

|    | 12.1.1 Si5345 Applications without a Crystal                          |     |

|    | 12.1.2 Si5345 Crystal Guidelines                                      |     |

|    | 12.1.3 Output Clocks                                                  |     |

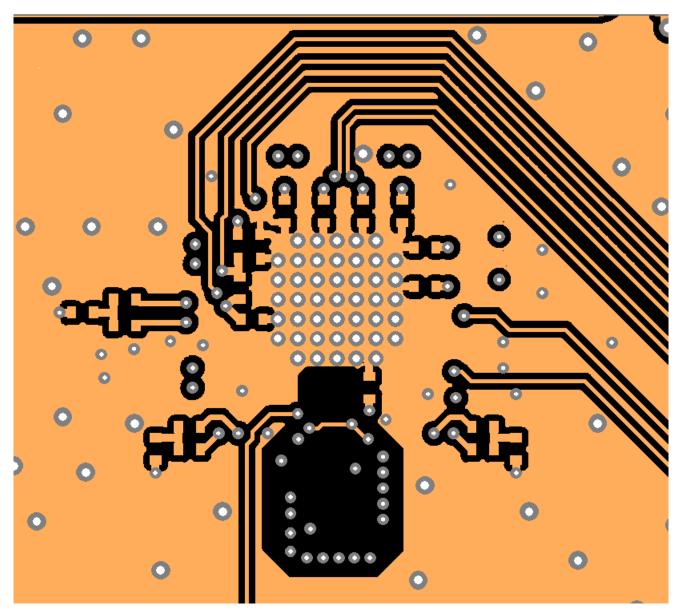

|    | 12.2 44-Pin QFN Si5344/42 Layout Recommendations                      | .71 |

|    | 12.2.1 Si5342/44 Applications without a Crystal                       |     |

|    | 12.2.2 Si5342/44 Crystal Guidelines                                   |     |

| 13 | 3. Power Management                                                   | 78  |

|    | 13.1 Power Management Features                                        | .78 |

|    | 13.2 Power Supply Recommendations                                     | .78 |

|    | 13.3 Power Supply Sequencing                                          | .79 |

|    | 13.4 Grounding Vias                                                   | .79 |

| 14. Si5345 Register Map                                               |       | 80  |

|-----------------------------------------------------------------------|-------|-----|

| 14.1 Base vs. Factory Preprogrammed Devices                           |       | .80 |

| 14.1.2 "Factory Preprogrammed" (Custom OPN) Devices                   |       |     |

| 14.2 Register Map Pages and Default Settings Values                   |       |     |

| 15. Si5345 Register Definitions                                       |       |     |

| 15.1 Page 0 Registers Si5345                                          |       |     |

| 15.2 Page 1 Registers Si5345                                          |       |     |

| 15.3 Page 2 Registers Si5345                                          |       | 101 |

| 15.4 Page 3 Registers Si5345                                          |       |     |

| 15.5 Page 4 Registers Si5345                                          |       |     |

| 15.6 Page 5 Registers Si5345                                          |       |     |

| 15.7 Page 9 Registers Si5345                                          |       | 120 |

| 15.8 Page A Registers Si5345                                          |       | 122 |

| 15.9 Page B Registers Si5345                                          |       | 123 |

| 16. Si5344 Register Definitions                                       |       | 125 |

| 16.1 Page 0 Registers Si5344                                          |       | 125 |

| 16.2 Page 1 Registers Si5344                                          |       | 140 |

| 16.3 Page 2 Registers Si5344                                          |       | 144 |

| 16.4 Page 3 Registers Si5344                                          |       | 151 |

| 16.5 Page 4 Registers Si5344                                          |       | 153 |

| 16.6 Page 5 Registers Si5344                                          |       | 154 |

| 16.7 Page 9 Registers Si5344                                          |       | 163 |

| 16.8 Page A Registers Si5344                                          |       | 165 |

| 16.9 Page B Registers Si5344                                          |       | 166 |

| 17. Si5342 Register Definitions                                       | <br>  | 168 |

| 17.1 Page 0 Registers Si5342                                          |       |     |

| 17.2 Page 1 Registers Si5342                                          |       |     |

| 17.3 Page 2 Registers Si5342                                          |       |     |

| 17.4 Page 3 Registers Si5342                                          |       |     |

| 17.5 Page 4 Registers Si5342                                          |       |     |

| 17.6 Page 5 Registers Si5342                                          |       |     |

| 17.7 Page 9 Registers Si5342                                          |       |     |

| 17.8 Page A Registers Si5342                                          |       |     |

| 17.9 Page B Registers Si5342                                          |       |     |

| 18. Setting the Differential Output Driver to Non-Standard Amplitudes |       |     |

| ·                                                                     | <br>• |     |

| 19. Revision History                                                  | <br>_ | 211 |

#### 1. Overview

The Si5345/44/42 jitter attenuating clock multipliers combine 4th generation DSPLL and MultiSynth™ technologies to enable any-frequency clock generation for applications that require the highest level of jitter performance. These devices are programmable via a serial interface with in-circuit programmable non-volatile memory (NVM) ensuring power up with a known frequency configuration. Free-run, synchronous, and holdover modes of operation are supported offering both automatic and manual input clock switching. The loop filter is fully integrated on-chip eliminating the risk of potential noise coupling associated with discrete solutions. Further, the jitter attenuation bandwidth is digitally programmable providing jitter performance optimization at the application level.

These devices are capable of generating any combination of output frequency from any input frequency within the specified input and output range.

#### 2. Work Flow Expectations with ClockBuilder Pro™ and the Register Map

This reference manual is to be used to describe all the functions and features of the parts in the product family with register map details on how to implement them. It is important to understand that the intent is for customers to use the ClockBuilder Pro software to provide the initial configuration for the device. Although the register map is documented, all the details of the algorithms to implement a valid frequency plan are fairly complex and are beyond the scope of this document. Real-time changes to the frequency plan and other operating settings are supported by the devices. However, describing all the possible changes is not a primary purpose of this document. Refer to Applications Notes and Knowledge Base article links within the ClockBuilder Pro GUI for information on how to implement the most common, real-time frequency plan changes.

The primary purpose of the software is that it saves having to understand all the complexities of the device. The software abstracts the details from the user to allow focus on the high level input and output configuration, making it intuitive to understand and configure for the end application. The software walks the user through each step, with explanations about each configuration step in the process to explain the different options available. The software will restrict the user from entering an invalid combination of selections. The final configuration settings can be saved, written to an EVB and a custom part number can be created for customers who prefer to order a factory preprogrammed device. The final register maps can be exported to text files, and comparisons can be done by viewing the settings in the register map described in this document.

#### 2.1 Family Product Comparison

Table 2.1 Product Selection Guide on page 7 lists a comparison of the different family members.

**Table 2.1. Product Selection Guide**

| Part Number | Number of Inputs | Number of MultiSynths | Number of Outputs | Package Type |

|-------------|------------------|-----------------------|-------------------|--------------|

| Si5342      | 4                | 2                     | 2                 | 44-QFN       |

| Si5344      | 4                | 4                     | 4                 | 44-QFN       |

| Si5345      | 4                | 5                     | 10                | 64-QFN       |

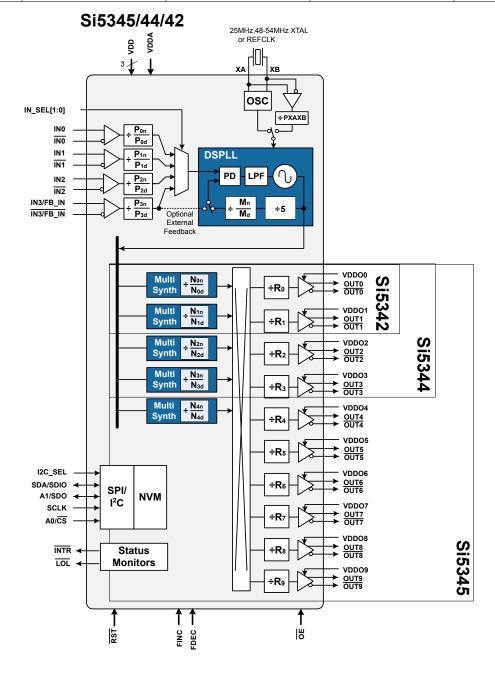

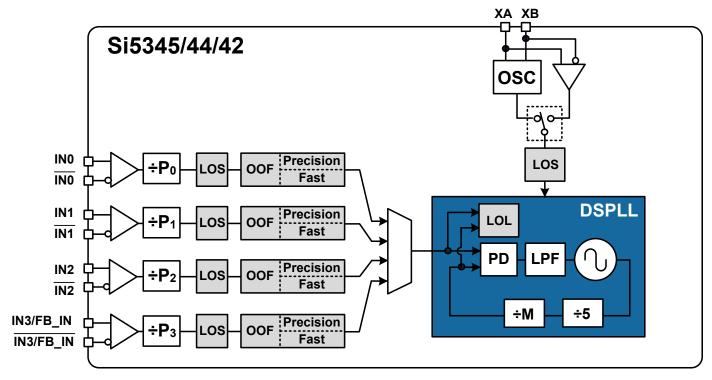

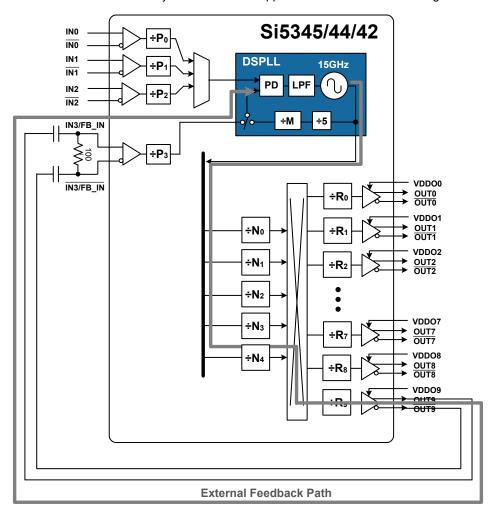

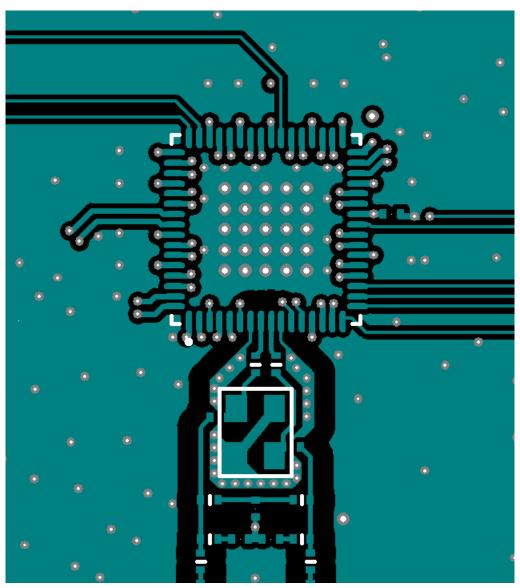

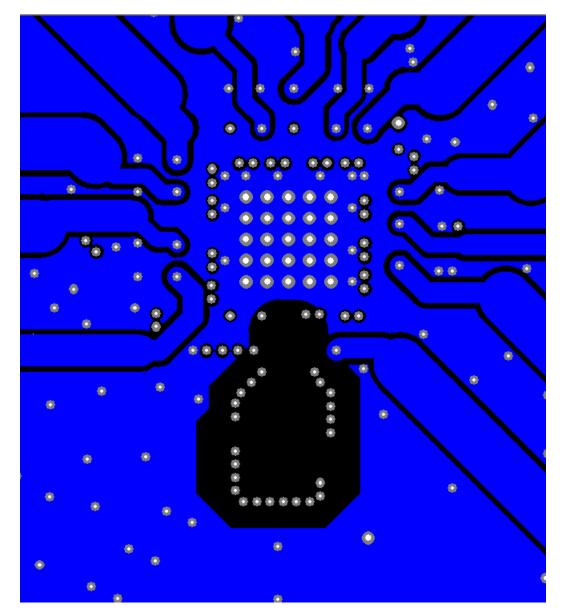

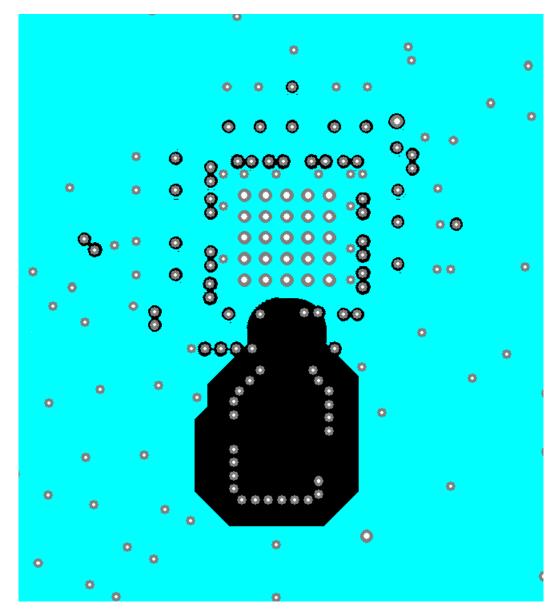

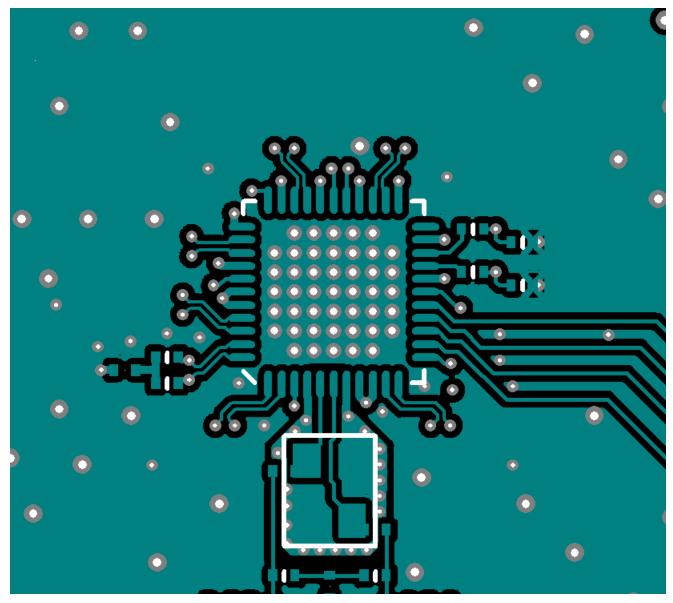

Figure 2.1. Block Diagram Si5345/44/42

#### 2.2 Available Software Tools and Support

ClockBuilder Pro is a software tool that is used for the Si5345/44/42 family and other product families, capable of configuring the timing chip in an intuitive, easy-to-use, step-by-step process. The software abstracts the details from the user to allow focus on the high level input and output configuration, making it intuitive to understand and configure for the end application. The software walks the user through each step, with explanations about each configuration step in the process to explain the different options available. The software will restrict the user from entering an invalid combination of selections. The final configuration settings can be saved, written to a device or written to the EVB and a custom part number can be created. This is all done with one software tool. ClockBuilder Pro integrates all the data sheets, application notes and information that might be helpful in one environment. It is intended that customers will use the software tool for the proper configuration of the device. Register map descriptions given in the document should not be the only source of information for programming the device. The complexity of the algorithms is embedded in the software tool.

#### 3. DSPLL and MultiSynth

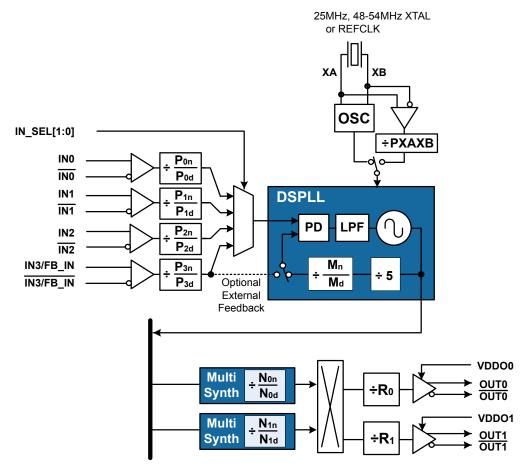

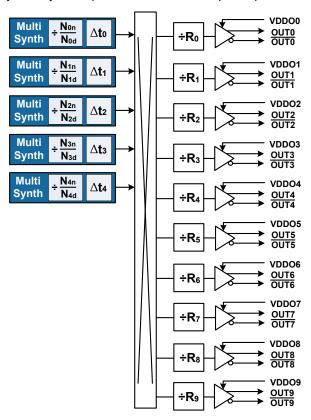

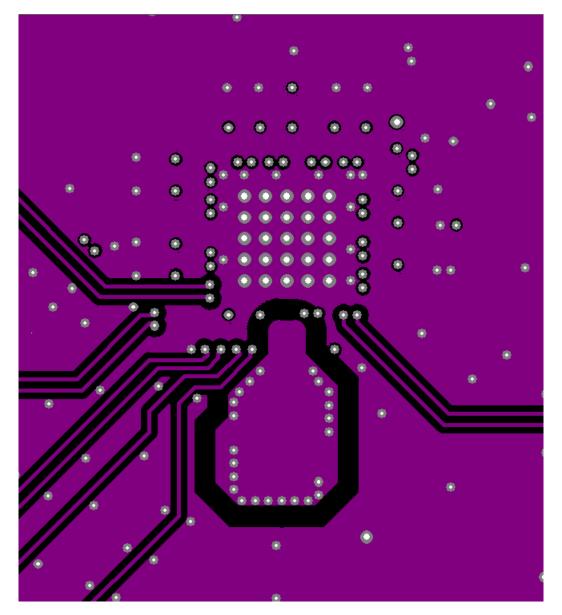

The DSPLL is responsible for input frequency translation, jitter attenuation and wander filtering. Fractional input dividers (Pxn/Pxd) allow the DSPLL to perform hitless switching between input clocks (INx) that are fractionally related. Input switching is controlled manually or automatically using an internal state machine. The oscillator circuit (OSC) provides a frequency reference which determines output frequency stability and accuracy while the device is in free-run or holdover mode. Note that a XTAL (or suitable XO reference on XA/XB) is always required and is the jitter reference for the device. The high-performance MultiSynth dividers (Nxn/Nxd) generate integer or fractionally related output frequencies for the output stage. A crosspoint switch connects any of the MultiSynth generated frequencies to any of the outputs. A single MultiSynth output can connect to two or more output drivers. Additional integer division (R) determines the final output frequency as shown in Figure 3.1 Si5342 DSPLL and Multisynth System Flow Diagram on page 9.

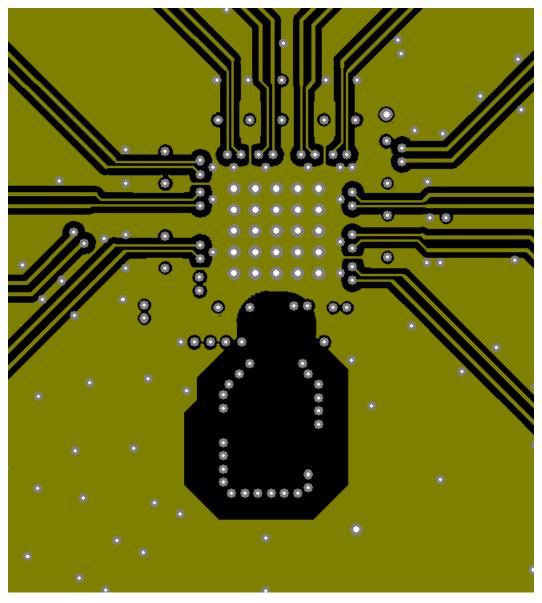

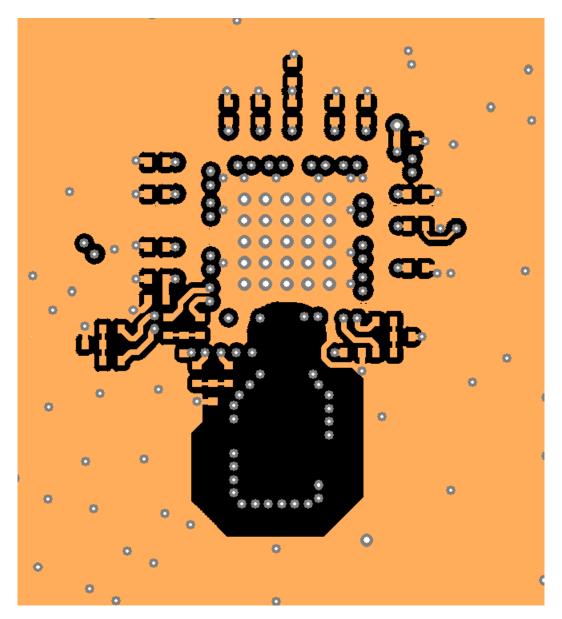

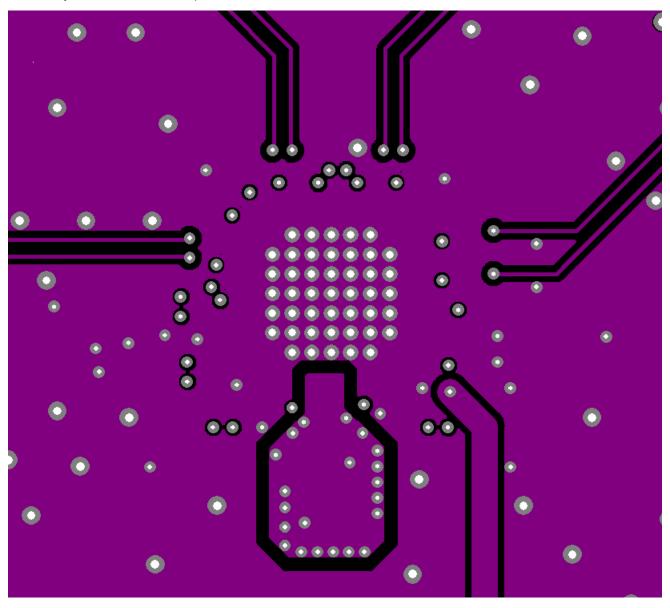

Figure 3.1. Si5342 DSPLL and Multisynth System Flow Diagram

The frequency configuration of the DSPLL is programmable through the SPI or I<sup>2</sup>C serial interface and can also be stored in non-volatile memory or RAM. The combination of fractional input dividers (Pn/Pd), fractional frequency multiplication (Mn/Md), fractional output MultiSynth division (Nn/Nd), and integer output division (Rn) allows the generation of virtually any output frequency on any of the outputs. All divider values for a specific frequency plan are easily determined using the ClockBuilder Pro software.

#### 3.1 Dividers

There are five divider classes within the Si5345/4/2. See Figure 1 for a block diagram that shows all of these dividers.

- 1. P-dividers: Wide range input dividers P3, P2, P1, P0

- MultiSynth divider: 48 bit numerator, 32 bit denominator, min value is 1

- · Practical range limited by phase detector and VCO range

- Each divider has an update bit that must be written to cause a newly written divider value to take effect.

- 2. Narrow range input divider: Pxaxb

- Only divides by 1, 2, 4, 8

- 3. Feedback M divider

- · MultiSynth divider

- · Integer or fractional divide values

- · 56 bit numerator, 32-bit denominator

- Practical range limited by phase detector and VCO range

- · Each divider has an update bit that must be written to cause a newly written divider value to take effect.

- 4. Output N divider

- · MultiSynth divider

- · Integer or fractional divide values

- · 44 bit numerator, 32 bit denominator

- Each divider has an update bit that must be written to cause a newly written divider value to take effect.

- 5. Output R divider

- · Only even integer divide values

- Min value is 2

- Maximum value is 2<sup>25</sup> 2

#### 3.2 DSPLL Loop Bandwidth

The DSPLL loop bandwidth determines the amount of input clock jitter attenuation and wander filtering. Register configurable DSPLL loop bandwidth settings in the range of 0.1 Hz to 4 kHz are available for selection. Since the loop bandwidth is controlled digitally, the DSPLL will always remain stable with less than 0.1 dB of peaking regardless of the loop bandwidth selection. The DSPLL loop bandwidth is set in registers 0x0508-0x050D and are determined using ClockBuilder Pro.

The higher the PLL bandwidth is set relative to the phase detector frequency ( $F_{pfd}$ ), the more chance that  $F_{pfd}$  will cause a spur in the Phase Noise plot of the output clock and increase the output jitter. To guarantee the best phase noise/jitter it is recommended that the normal PLL bandwidth be kept less than  $F_{pfd}$ /160 although ratios of  $F_{pfd}$ /100 will typically work fine.

Table 3.1. PLL Bandwidth Registers

| Register Name | Hex Address [Bit Field] | Function                                                                                                          |

|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------|

| BWx_PLL       |                         | Determines the loop BW for the DSPLL. This is set by CBPro. See CBPro for a correlation of bandwidths and values. |

#### 3.2.1 Fastlock Feature

Selecting a low DSPLL loop bandwidth (e.g. 0.1 Hz) will generally lengthen the lock acquisition time. The Fastlock feature allows setting a temporary Fastlock Loop Bandwidth that is used during the lock acquisition process to reduce lock time. Higher Fastlock loop bandwidth settings will enable the DSPLLs to lock faster. Fastlock Bandwidth settings in the range from 100 Hz up to 4 kHz are available for selection. Once lock acquisition has completed, the DSPLL's loop bandwidth will automatically revert to the DSPLL Loop Bandwidth setting. The Fastlock feature can be enabled or disabled independently by register control. If enabled, when LOL is asserted Fastlock will be automatically enabled. When LOL is no longer asserted, Fastlock will be automatically disabled.

Note: This update bit will latch new values for Loop, Fastlock, and Holdover bandwidths simultaneously.

Table 3.2. Fastlock Registers

| Register Name    | Hex Address [Bit Field] | Function                                        |

|------------------|-------------------------|-------------------------------------------------|

| FASTLOCK_AUTO_EN | 0x052B[0]               | Auto Fastlock Enable/Disable                    |

| FASTLOCK_MAN     | 0x052B[1]               | 0 for normal operation,<br>1 to force fast lock |

| FASTLOCK_BW_PLL  | 0x050E[7:0]-0x0513[7:0] | Fastlock BW selection.                          |

The loss of lock (LOL) feature is a fault monitoring mechanism. Details of the LOL feature can be found in 5.3.3 Loss of Lock (LOL) Fault Monitoring.

#### 3.2.2 Holdover Exit Bandwidth

In addition to the operating loop and fastlock bandwidths, there is also a user-selectable bandwidth when exiting holdover and locking or relocking to an input clock, available when ramping is disabled (HOLD\_RAMP\_BYP = 1). CBPro sets this value equal to the loop bandwidth by default.

Note: The BW UPDATE bit will latch new values for Loop, Fastlock, and Holodver bandwidths simultaneously.

Table 3.3. DSPLL Holdover Exit Bandwidth Registers

| Register Name | Hex Address | Function                                                                                                                                                      |

|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOLDEXIT_BW   |             | Determines the Holdover Exit BW for the DSPLL. Parameters are generated by ClockBuilder Pro. See CBPro for the generated values and corresponding bandwidths. |

#### 4. Modes of Operation

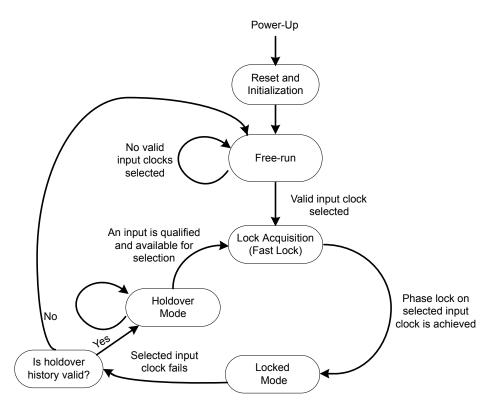

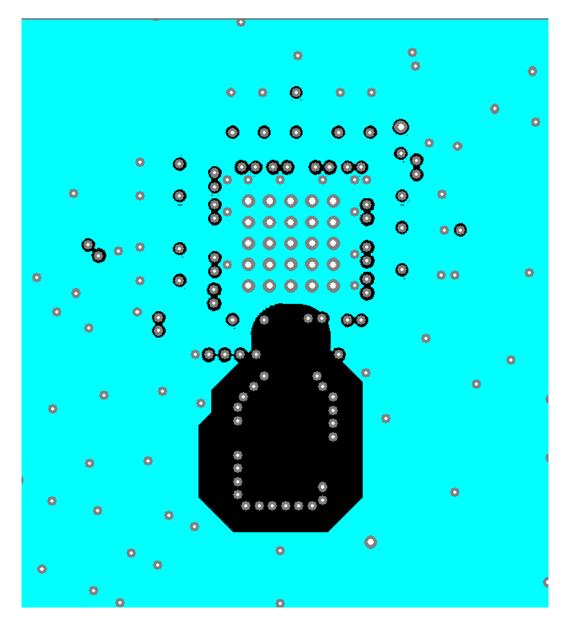

After initialization the DSPLL will operate in one of the following modes: Free-run, lock-acquisition, locked, or holdover. See Figure 4.1 Modes of Operation on page 12 below for the state diagram showing the modes of operation. The following sections describe each of these modes in greater detail.

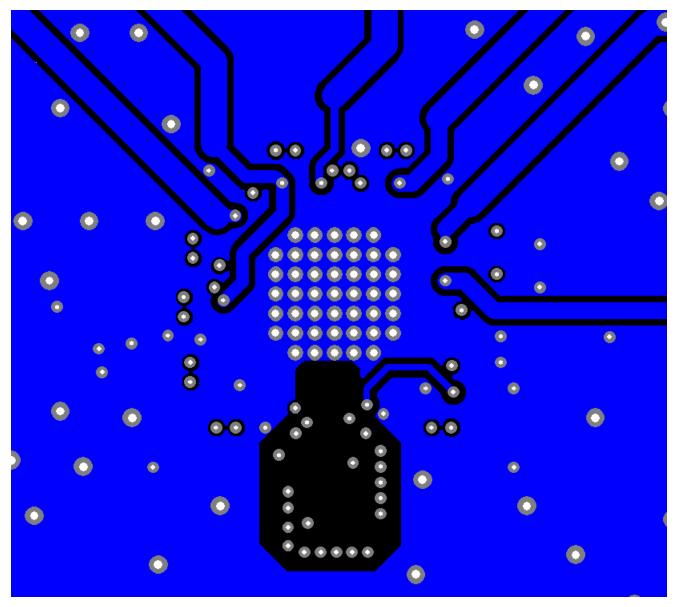

Figure 4.1. Modes of Operation

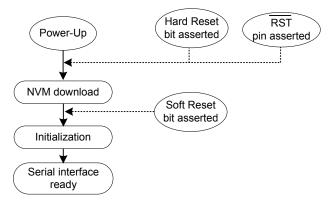

#### 4.1 Reset and Initialization

Once power is applied, the device begins an initialization period where it downloads default register values and configuration data from NVM and performs other initialization tasks. Communicating with the device through the serial interface is possible once this initialization period is complete. No clocks will be generated until initialization is complete.

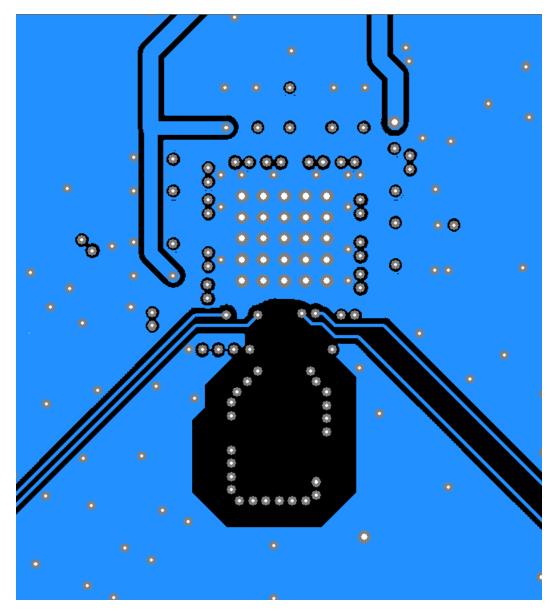

There are two types of resets available. A hard reset is functionally similar to a device power-up. All registers are restored to the values stored in NVM, and all circuits, including the serial interface, are restored to their initial state. A hard reset is initiated using the RST pin or by asserting the hard reset bit. A soft reset bypasses the NVM download. It is simply used to initiate register configuration changes. Table 4.1 Reset Registers on page 13 lists the reset and control registers.

Figure 4.2. Si5345/44/42 Memory Configuration

Table 4.1. Reset Registers

| Register Name | Hex Ad-<br>dress [Bit<br>Field] | Function                                                                                                        |

|---------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------|

| HARD_RST      | 0x001E[1]                       | Performs the same function as power cycling the device. All registers will be restored to their default values. |

| SOFT_RST      | 0x001C[0]                       | Performs a soft reset. Initiates register configuration changes.                                                |

Figure 4.3. Initialization from Hard Reset and Soft Reset

The Si5345/44/42 is fully configurable using the serial interface (I<sup>2</sup>C or SPI). At power up the device downloads its default register values from internal non-volatile memory (NVM). Application specific default configurations can be written into NVM allowing the device to generate specific clock frequencies at power-up. Writing default values to NVM is in-circuit programmable with normal operating power supply voltages applied to its VDD (1.8V) and VDDA (3.3 V) pins.

#### 4.2 Dynamic PLL Changes

It is possible for a PLL to become unresponsive (i.e., lose lock indefinitely) when it is dynamically reprogrammed or changed via the serial port. Reprogramming/changing the N divider does not affect the PLL. Any change that causes the VCO frequency to change by more than 250 ppm since Power-up, NVM download, or SOFT\_RST requires the following special sequence of writes. Changes to the following registers require the this special sequence of writes:

- PXAXB

- MXAXB\_NUM

- MXAXB DEN

- M NUM

- M DEN

- 1. First, write in the preamble

Write 0x0B24 = 0xC0

Write 0x0B25 = 0x00

Write 0x0540 = 0x01 (NOTE: for all new designs it is recommend that this register be written as part of the preamble. In some rare cases, omitting this write may result in a one-time LOL occurrence. However, if this issue has not occurred with your current frequency plan it is not likely to occur)

- 2. Wait 300 ms.

- 3. Then perform the desired register modifications

- 4. Write SOFT\_RST 0x001C[0] = 1

- 5. Write the post-amble

Write 0x0540 = 0x00 (NOTE: for all new designs it is recommend that this register be written as part of the post-amble. In some rare cases, omitting this write may result in a one-time LOL occurrence. However, if this issue has not occurred with your current frequency plan it is not likely to occur)

Write 0x0B24 = 0xC3

Write 0x0B25 = 0x02

**Note:** This programming sequence applies only to Rev D and later and has changed for revision D and later from what it was in the earlier revisions. The preamble and postamble values for updating certain registers during device operation are different for earlier revisions. Either the new or old values below may be written to revision D or later devices without issue. No system software changes are necessary for legacy systems. When writing old values, note that reading back these registers will not give the written old values, but will reflect the new values. Skyworks recommends using the new values for all revision D (described above) and later designs, since the write and read values will match. Please contact Skyworks if you need information about an earlier revision. Please always ensure to use the correct sequence for the correct revision of the device. Also check for the latest information online. This information is updated from time to time. The latest information is always posted online.

#### 4.3 NVM Programming

Devices have two categories of non-volatile memory: user NVM and factory (Skyworks) NVM. Each type is segmented into NVM banks. There are three user NVM banks, one of which is used for factory programming (whether a base part or an Orderable Part Number). User NVM can be therefore be burned in the field up to two times. Factory NVM cannot be modified, and contains fixed configuration information for the device.

The ACTIVE\_NVM\_BANK device setting can be used to determine which user NVM bank is currently being used and therefore how many banks, if any, are available to burn. The following table describes possible values:

| Active NVM BANK Value (Decimal) | Number of User Banks Burned | Number of User Banks<br>Available to Burn |

|---------------------------------|-----------------------------|-------------------------------------------|

| 3 (factory state)               | 1                           | 2                                         |

| 15                              | 2                           | 1                                         |

| 63                              | 3                           | 0                                         |

Note: While polling DEVICE\_READY during the procedure below, the following conditions must be met in order to ensure that the correct values are written into the NVM:

- VDD and VDDA power must both be stable throughout the process.

- No additional registers may be written or read during DEVICE\_READY polling. This includes the PAGE register at address 0x01. DEVICE\_READY is available on every register page, so no page change is needed to read it.

- Only the DEVICE READY register (0xFE) should be read during this time.

The procedure for writing registers into NVM is as follows:

- 1. Write all registers as needed. Verify device operation before writing registers to NVM.

- 2. You may write to the user scratch space (Registers 0x026B to 0x0272 DESIGN\_ID0-DESIGN\_ID7) to identify the contents of the NVM bank.

- 3. Write 0xC7 to NVM\_WRITE register.

- 4. Poll DEVICE READY until DEVICE READY=0x0F.

- 5. Set NVM READ BANK 0x00E4[0]=1. This will load the NVM contents into non-volatile memory.

- 6. Poll DEVICE READY until DEVICE READY=0x0F.

- 7. Read ACTIVE\_NVM\_BANK and verify that the value is the next highest value in the table above. For example, from the factory it will be a 3. After NVM WRITE, the value will be 15.

Alternatively, steps 5 and 6 can be replaced with a Hard Reset, either by RSTb pin, HARD\_RST register bit, or power cycling the device to generate a POR. All of these actions will load the new NVM contents back into the device registers.

The ClockBuilder Pro Field Programmer kit is a USB attached device to program supported devices either in-system (wired to your PCB) or in-socket (by purchasing the appropriate field programmer socket). ClockBuilder Pro software is then used to burn a device configuration (project file). Learn more at https://www.skyworksinc.com/en/products/timing/evaluation-kits/general/clockbuilder-pro-field-programmer.

**Table 4.2. NVM Programming Registers**

| Register Name   | Hex Address | Function                                                                 |

|-----------------|-------------|--------------------------------------------------------------------------|

|                 | [Bit Field] |                                                                          |

| ACTIVE_NVM_BANK | 0x00E2[7:0] | Identifies the active NVM bank.                                          |

| NVM_WRITE       | 0x00E3[7:0] | Initiates an NVM write when written with value 0xC7.                     |

| NVM_READ_BANK   | 0x00E4[0]   | Download register values with content stored in NVM.                     |

| DEVICE_READY    | 0x00FE[7:0] | Indicates that the device is ready to accept commands when value = 0x0F. |

**Warning:** Any attempt to read or write any register other than DEVICE\_READY before DEVICE\_READY reads as 0x0F may corrupt the NVM programming and may corrupt the register contents, as they are read from NVM. Note that this includes accesses to the PAGE register.

#### 4.4 Free Run Mode

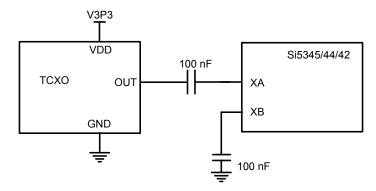

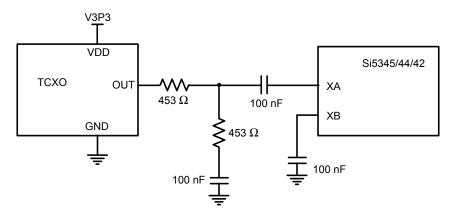

The DSPLL will automatically enter freerun mode once power is applied to the device and initialization is complete. The frequency accuracy of the generated output clocks in freerun mode is entirely dependent on the frequency accuracy of the external crystal or reference clock on the XA/XB pins. For example, if the crystal frequency is ±100 ppm, then all the output clocks will be generated at their configured frequency ±100 ppm in freerun mode. Any drift of the crystal frequency will be tracked at the output clock frequencies. A TCXO or OCXO is recommended for applications that need better frequency accuracy and stability while in freerun or holdover modes. Because there is little or no jitter attenuation from the XAXB pins to the clock outputs, a low-jitter XAXB source will be needed for low-jitter clock outputs.

#### 4.5 Acquisition Mode

The device monitors all inputs for a valid clock. If at least one valid clock is available for synchronization, the DSPLL will automatically start the lock acquisition process. If the fast lock feature is enabled, the DSPLL will acquire lock using the Fastlock Loop Bandwidth setting and then transition to the DSPLL Loop Bandwidth setting when lock acquisition is complete. During lock acquisition the outputs will generate a clock that follows the VCO frequency change as it pulls-in to the input clock frequency.

#### 4.6 Locked Mode

Once locked, the DSPLL will generate output clocks that are both frequency and phase locked to its selected input clock. At this point any XTAL frequency drift will typically not affect the output frequency. A loss of lock pin (LOL) and status bit indicate when lock is achieved. See 5.3.3 Loss of Lock (LOL) Fault Monitoring for more details on the operation of the loss of lock circuit.

#### 4.7 Holdover Mode

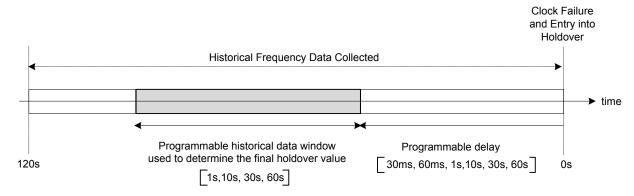

The DSPLL if programmed for holdover mode will automatically enter Holdover mode when the selected input clock becomes invalid and no other valid input clocks are available for selection. It uses an averaged input clock frequency as its final holdover frequency to minimize the disturbance of the output clock phase and frequency when an input clock suddenly fails. The holdover circuit stores up to 120 seconds of historical frequency data while locked to a valid clock input. The final averaged holdover frequency value is calculated from a programmable window within the stored historical frequency data. Both the window size and the delay are programmable as shown in the figure below. The window size determines the amount of holdover frequency averaging. This delay value allows recent frequency information to be ignored for Holdover in cases where the input clock source frequency changes as it is removed.

Figure 4.4. Programmable Holdover Window

When entering Holdover, the DSPLL will pull its output clock frequency to the calculated averaged holdover frequency. While in Holdover, the output frequency drift is entirely dependent on the external crystal or external reference clock connected to the XAXB pins. If the clock input becomes valid, the DSPLL will automatically exit the Holdover mode and re-acquire lock to the new input clock. This process involves pulling the output clock frequency to achieve frequency and phase lock with the input clock. This pull-in process is Glitchless and its rate is controlled by the DSPLL bandwidth or the Fastlock bandwidth, if Fastlock is enabled. These options are register programmable.

The recommended mode of exit from holdover is a ramp in frequency. Just before the exit begins, the frequency difference between the output frequency while in holdover and the desired, new output frequency is measured. It is quite possible (even likely) that the new output clock frequency will not be the same as the holdover output frequency because the new input clock frequency might have changed and the holdover history circuit may have changed the holdover output frequency. The ramp logic calculates the difference in frequency between the holdover frequency and the new, desired output frequency. Using the user selected ramp rate, the correct ramp time is calculated. The output ramp rate is then applied for the correct amount of time so that when the ramp ends, the output frequency will be the desired new frequency. Using the ramp, the transition between the two frequencies is smooth and linear. The ramp rate can be selected to be very slow (0.2 ppm/sec), very fast (40,000 ppm/sec) or any of approximately 40 values that are in between. The loop BW values do not limit or affect the ramp rate selections and vice versa. CBPro defaults to ramped exit from holdover. Ramped exit from holdover is also used for ramped input clock switching. See 5.2.3 Ramped Input Switching for more information.

As shown in Figure 4.1 Modes of Operation on page 12, the Holdover and Freerun modes are closely related. The device will only enter Holdover if a valid clock has been selected long enough for the holdover history to become valid, i.e., HOLD\_HIST\_VALID = 1. If the clock fails before the combined HOLD\_HIST\_LEN + HOLD\_HIST\_DELAY time has been met, HOLD\_HIST\_VALID = 0 and the device will enter Freerun mode instead. Reducing the HOLD\_HIST\_LEN and HOLD\_HIST\_DELAY times will allow Holdover in less time, limited by the source clock failure and wander characteristics. Note that the Holdover history accumulation is suspended when the input clock is removed and resumes accumulating when a valid input clock is again presented to the DSPLL.

| Register Name   | Hex Address<br>[Bit Field] | Function                            |

|-----------------|----------------------------|-------------------------------------|

| Holdover Status |                            |                                     |

| HOLD            | 0x000E[5]                  | DSPLL Holdover status indicator.    |

|                 |                            | 0: Normal Operation                 |

|                 |                            | 1: In Holdover/Freerun Mode:        |

|                 |                            | HOLD_HIST_VALID = 0 ? Freerun Mode  |

|                 |                            | HOLD_HIST_VALID = 1 ? Holdover Mode |

Table 4.3. Holdover Mode Control Registers

| Register Name      | Hex Address<br>[Bit Field] | Function                                                                                                                                                                                                    |

|--------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HOLD_FLG           | 0x0013[5]                  | Holdover indicator sticky flag bit. Remains asserted after the indicator bit shows a fault until cleared by the user. Writing a 0 to the flag bit will clear it if the indicator bit is no longer asserted. |

| HOLD_INTR_MSK      | 0x0019[5]                  | Masks Holdover/Freerun from generating INTR interrupt.                                                                                                                                                      |

|                    |                            | 0: Allow Holdover/Freerun interrupt (default)                                                                                                                                                               |

|                    |                            | 1: Mask (ignore) Holdover/Freerun for interrupt                                                                                                                                                             |

| HOLD_HIST_VALID    | 0x053F[1]                  | Holdover historical frequency data valid.                                                                                                                                                                   |

|                    |                            | 0: Incomplete Holdover history, Freerun mode available                                                                                                                                                      |

|                    |                            | 1: Valid Holdover history, Holdover mode available                                                                                                                                                          |

|                    | Но                         | oldover Control and Settings                                                                                                                                                                                |

| HOLD_HIST_LEN      | 0x052E[4:0]                | Window Length time for historical average frequency used in Holdover mode. Window Length in seconds (s):                                                                                                    |

|                    |                            | Window Length = $((2^{LEN}) - 1) \times 268 \text{ ns}$                                                                                                                                                     |

| HOLD_HIST_DELAY    | 0x052F[4:0]                | Delay Time to ignore data for historical average frequency in Holdover mode. Delay Time in seconds (s):                                                                                                     |

|                    |                            | Delay Time (s) = (2 <sup>DELAY</sup> ) x 268 ns                                                                                                                                                             |

| FORCE_HOLD         | 0x0535[0]                  | Force the device into Holdover mode. Used to hold the device output clocks while retraining an upstream input clock.                                                                                        |

|                    |                            | 0: Normal Operation                                                                                                                                                                                         |

|                    |                            | 1: Force Holdover/Freerun Mode:                                                                                                                                                                             |

|                    |                            | HOLD_HIST_VALID = 0 ? Freerun Mode                                                                                                                                                                          |

|                    |                            | HOLD_HIST_VALID = 1 ? Holdover Mode                                                                                                                                                                         |

|                    |                            | Holdover Exit Control                                                                                                                                                                                       |

| HOLD_RAMP_BYP      | 0x052C[3]                  | Holdover Exit Ramp Bypass                                                                                                                                                                                   |

|                    |                            | 0: Use Ramp when exiting from Holdover (default)                                                                                                                                                            |

|                    |                            | 1: Use Holdover/Fastlock/Loop bandwidth when exiting from Holdover                                                                                                                                          |

| HOLDEXIT_BW_SEL0   | 0x059B[6]                  | Select the exit bandwidth from Holdover when ramped exit is not selected (HOLD_RAMP_BYP = 1).                                                                                                               |

|                    |                            | 00: Use Fastlock bandwidth on Holdover exit                                                                                                                                                                 |

|                    |                            | 01: Use Holdover Exit bandwidth on Holdover exit (default)                                                                                                                                                  |

|                    |                            | 10, 11: Use Normal Loop bandwidth on Holdover exit                                                                                                                                                          |

| HOLDEXIT_BW_SEL1   | 0x052C[4]                  | Select the exit bandwidth from Holdover when ramped exit is not selected (HOLD_RAMP_BYP = 1).                                                                                                               |

|                    |                            | 00: Use Fastlock bandwidth on Holdover exit                                                                                                                                                                 |

|                    |                            | 01: Use Holdover Exit bandwidth on Holdover exit (default)                                                                                                                                                  |

|                    |                            | 10, 11: Use Normal Loop bandwidth on Holdover exit                                                                                                                                                          |

| RAMP_STEP_INTERVAL | 0x052C[7:5]                | Time Interval of the frequency ramp steps when ramping between inputs or exiting holdover.                                                                                                                  |

| RAMP_STEP_SIZE     | 0x05A6[2:0]                | Size of the frequency ramp steps when ramping between inputs or exiting holdover.                                                                                                                           |

#### 5. Clock Inputs

The Si5342/44/45 support 4 inputs that can be used to synchronize to the internal DSPLL.

#### 5.1 Inputs (IN0, IN1, IN2, IN3)

The inputs accept both standard format inputs and low-duty-cycle pulsed CMOS clocks. Input selection from CLK\_SWITCH\_MODE can be manual (pin or register controlled) or automatic with user definable priorities. Register 0x052A is used to select pin or register control, and to configure the input as shown below in Table 5.1 Input Selection Configuration on page 19.

Table 5.1. Input Selection Configuration

| Register Name   | Hex Address<br>[Bit Field] | Function                                                                                                                     |  |

|-----------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| CLK_SWITCH_MODE | 0x0536[1:0]                | Selects manual or automatic switching modes. Automatic mode can be revertive or non-revertive. Selections are the following: |  |

|                 |                            | 00 Manual,01 Automatic non-revertive                                                                                         |  |

|                 |                            | 02 Automatic revertive, 03 Reserved                                                                                          |  |

| IN_SEL_REGCTRL  | 0x052A [0]                 | 0 for pin controlled clock selection                                                                                         |  |

|                 |                            | 1 for register controlled clock selection                                                                                    |  |

| IN_SEL          | 0x052A [2:1]               | 0 for IN0, 1 for IN1,                                                                                                        |  |

|                 |                            | 2 for IN2, 3 for IN3 (or FB_IN)                                                                                              |  |

#### 5.1.1 Manual Input Switching

In manual mode, CLK SWITCH MODE=0x00.

Input switching can be done manually using the IN\_SEL[1:0] device pins from the package or through register 0x052A IN\_SEL[2:1]. Bit 0 of register 0x052A determines if the input selection is pin selectable or register selectable. The default is pin selectable. The following table describes the input selection on the pins. Note that when Zero Delay Mode is enabled, the FB\_IN pins will become the feedback input and IN3 therefore is not available as a clock input. Also, in Zero Delay Mode, ZDM\_EN must be set and register based input clock selection must be done with ZDM\_IN\_SEL. If there is no clock signal on the selected input, the device will automatically enter free-run or holdover mode.

Table 5.2. Manual Input Selection using IN SEL[1:0] Pins

| IN_SEL[1:0] DEVICE PINS | Zero Delay Mode Disabled | Zero Delay Mode Enabled |

|-------------------------|--------------------------|-------------------------|

| 00                      | IN0                      | IN0                     |

| 01                      | IN1                      | IN1                     |

| 10                      | IN2                      | IN2                     |

| 11                      | IN3                      | Reserved                |

#### 5.1.2 Automatic Input Selection

In automatic mode CLK SWITCH MODE = 0x01 (non-revertive) or 0x02 (revertive)

An automatic input selection is available in addition to the above mentioned manual switching option described in 5.1.1 Manual Input Switching. In automatic mode, the selection criteria is based on input clock qualification, input priority and the revertive option. The IN\_SEL[1:0] pins or IN\_SEL[2:1] register bits are not used in automatic input selection. Also, only input clocks that are valid (i.e., with no active alarms) can be selected by the automatic clock selection. If there are no valid input clocks available the DSPLL will enter the holdover mode. With revertive switching enabled, the highest priority input with a valid input clock is always selected. If an input with a higher priority becomes valid then an automatic switchover to that input will be initiated. With non-revertive switching, the active input will always remain selected while it is valid. If it becomes invalid an automatic switchover to a valid input with the highest priority will be initiated.

Table 5.3. Registers for Automatic Input Selection

| Register Name       | Hex Address [Bit<br>Field] | Function                                                                                                                                                                                              |  |

|---------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLK_SWITCH_MOD<br>E | 0x0536[1:0]                | Selects manual or automatic switching modes. Automatic mode can be revertive or non-revertive. Selections are the following: 00 Manual,01 Automatic non-revertive 02 Automatic revertive, 03 Reserved |  |

| ZDM_EN              | 0x0487[0]                  | 0: disable zero delay mode 1: enable zero delay mode                                                                                                                                                  |  |

| ZDM_IN_SEL          | 0x0487[2:1]                | Selects the input when in manual register controlled mode when zero delay mode is enabled. Selections are IN0, IN1, IN2. A register value of 3 is not allowed.                                        |  |

| ZDM_AUTOSW_EN       | 0x0487[4]                  | automatic switching disabled for zero-delay mode     automatic input switching enabled and input clock selection governed by automatic input switching engine                                         |  |

| IN0_PRIORITY        | 0x0538[2:0]                |                                                                                                                                                                                                       |  |

| IN1_PRIORITY        | 0x0538[6:4]                | IN0, IN1, IN2, IN3 priority select for the automatic selection state machine. Priority                                                                                                                |  |

| IN2_PRIORITY        | 0x0539[2:0]                | selections are 1,2,3,4, or zero for no priority.                                                                                                                                                      |  |

| IN3_PRIORITY        | 0x0539[6:4]                |                                                                                                                                                                                                       |  |

| IN_LOS_MSK          | 0x0537[3:0]                | Determines the LOS status for IN3,2,1,0 and is used in determining a valid clock for automatic input selection                                                                                        |  |

|                     |                            | 0 to use LOS in clock selection logic, 1 to mask LOS from the clock selection logic                                                                                                                   |  |

| IN_OOF_MSK          | 0x0537[7:4]                | Determines the OOF status for IN3,2,1,0 and is used in determining a valid clock for the automatic input selection                                                                                    |  |

|                     |                            | 0 to use OOF in the clock selection logic, 1 to mask the OOF from the clock selection logic                                                                                                           |  |

When in zero delay mode (ZDM\_EN (0x0487[0]) the phase difference between the output, which is connected to the selected input, will be nulled to zero. However the IO delay variation will substantially increase in ZDM mode if the Fpfd is below 128 kHz. When in zero delay mode, the DSPLL must have the phase buildout turned off for input switching or else the IO delay can change on each input switch. Manual control of the input clock selection is by either pin or register and also depends upon the device being in zero delay mode or not. See Table 5.4 Register 0x0949 Clock Input Control and Configuration on page 22.

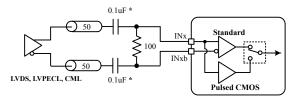

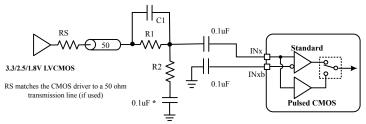

#### 5.2 Types of Inputs

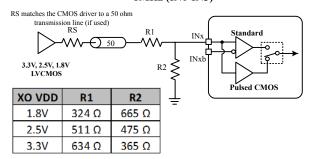

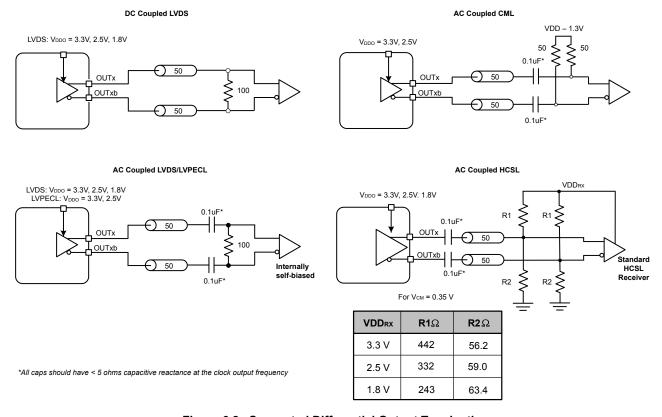

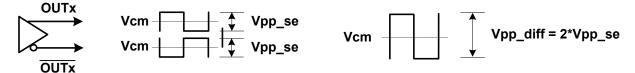

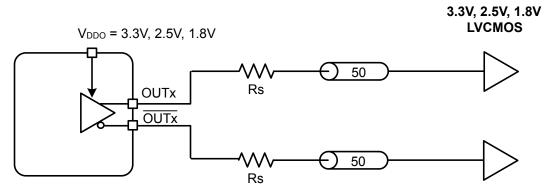

Each of the four different inputs IN0–IN3 can be configured as standard LVDS, LVPECL, HCL, CML, and single-ended LVCMOS formats, or as a low duty cycle pulsed CMOS format. The standard format inputs have a nominal 50% duty cycle, must be ac-coupled and use the "Standard" Input Buffer selection as these pins are internally dc-biased to approximately 0.83 V. The pulsed CMOS input format allows pulse-based inputs, such as frame-sync and other synchronization signals, having a duty cycle much less than 50%. These pulsed CMOS signals are dc-coupled and use the "Pulsed CMOS" Input Buffer selection. In all cases, the inputs should be terminated near the device input pins as shown in Figure 5.1 Input Termination for Standard and Pulsed CMOS Inputs on page 21. The resistor divider values given below will work with up to 1 MHz pulsed inputs.

#### Standard AC-Coupled Differential (IN0-IN3)

\* These caps should have < ~5 ohms capacitive reactance at the clock input frequency.

#### Standard AC-Coupled Single-Ended (IN0-IN3)

Only when 3.3V LVCMOS driver is present, use R2 = 845 ohm and R1 = 267 ohm if needed to keep the signal at INx < 3.6 Vpp\_se. Including C1 = 6 pf may improve the output jitter due to faster input slew rate at INx. If attenuation is not needed for Inx<3.6Vppse, make R1 = 0 ohm and omit C1, R2 and the capacitor below R2. C1, R1, and R2 should be physically placed as close as practicle to the device input pins. \*This cap should have less than ~20 ohms of capacitive reactance at the clock input frequency

## DC-Coupled Pulsed CMOS only for Frequencies < 1MHz (IN0-IN3)

Note: See Datasheet for input clock specifications

Figure 5.1. Input Termination for Standard and Pulsed CMOS Inputs

Note: Floating clock inputs are noise sensitive. Add a cap to non-CMOS unused clock inputs.

Input clock buffers are enabled by setting the IN\_EN 0x0949[3:0] bits appropriately for IN3 through IN0. Unused clock inputs may be powered down and left unconnected at the system level. For standard mode inputs, both input pins must be properly connected as shown in Figure 5.1 Input Termination for Standard and Pulsed CMOS Inputs on page 21 above, including the "Standard AC Coupled Single Ended" case. In Pulsed CMOS mode, it is not necessary to connect the inverting INx input pin. To place the input buffer into Pulsed CMOS mode, the corresponding bit must be set in IN PULSED CMOS EN 0x0949[7:4] for IN3 through IN0.

Table 5.4. Register 0x0949 Clock Input Control and Configuration

| Register Name     | Hex Address<br>[Bit Field] | Function                                                                                      |

|-------------------|----------------------------|-----------------------------------------------------------------------------------------------|

| IN_EN             | 0x0949[3:0]                | Enables for the four inputs clocks, IN0 through IN3.                                          |

|                   |                            | 1 to enable.                                                                                  |

| IN_PULSED_CMOS_EN | 0x0949[7:4]                | Selects CMOS or differential receiver for IN3, IN2, IN1, IN0. Defaults to differential input. |

|                   |                            | Differential = 0, CMOS = 1                                                                    |

#### 5.2.1 Unused Inputs

Unused inputs can be disabled and left unconnected when not in use. Register 0x0949[3:0] defaults the input clocks to being enabled. Clearing the unused input bits will disable them.

#### 5.2.2 Hitless Input Switching with Phase Buildout

Phase buildout, also referred to as hitless switching, prevents a phase change from propagating to the output when switching between two clock inputs with the exact same frequency and a fixed phase relationship (i.e., they are phase/frequency locked, but with a non-zero phase difference). When phase buildout is enabled, the DSPLL absorbs the phase difference between the two input clocks during a clock switch. When phase buildout is disabled, the phase difference between the two inputs is propagated to the output at a rate determined by the DSPLL loop bandwidth. It supports a minimum input frequency of 8 kHz, but if a fractional P input divider is used, the input frequency must be 300 MHz or higher in order to ensure proper operation. Note that hitless switching is not available in zero delay mode.

Table 5.5. Hitless Switching Enable Bit

|        | Hex Ad-<br>dress [Bit<br>Field] | Function                                           |

|--------|---------------------------------|----------------------------------------------------|

| HSW_EN | 0x0536[2]                       | Hitless switching is enabled = 1, or disabled = 0. |

#### 5.2.3 Ramped Input Switching

If switching between input clocks that are not exactly the same frequency (i.e. are plesiochronous), ramped switching should be enabled to ensure a smooth transition between the two inputs. In this situation, it is also advisable to enable phase buildout to minimize the input-to-output clock skew after the clock switch ramp has completed.

When ramped clock switching is enabled, the Si5345/44/42 will very briefly go into holdover and then immediately exit from holdover. This means that ramped switching will behave the same as an exit from holdover. This is particularly important when switching between two input clocks that are not the same frequency because the transition between the two frequencies will be smooth and linear. Ramped switching should be turned off when switching between input clocks that are always frequency-locked (i.e., are the same exact frequency). Because ramped switching avoids frequency transients and overshoot when switching between clocks that are not the same frequency, CBPro defaults to ramped clock switching. The same ramp rate settings are used for both exit from holdover and clock switching. For more information on ramped exit from holdover including the ramp rate, see 4.7 Holdover Mode.

Table 5.6. Ramped Input Switching Control Registers

| Setting Name Hex Address [Bit Field] |             | Function                                     |  |

|--------------------------------------|-------------|----------------------------------------------|--|

| RAMP_SWITCH_EN                       | 0x05A6[3]   | Enable frequency ramping on an input switch. |  |

| HSW_MODE                             | 0x053A[1:0] | Input switching mode select.                 |  |

#### 5.2.4 Hitless Switching, LOL (loss of lock) and Fastlock

When doing a clock switch between clock inputs that are frequency locked, LOL might momentarily be asserted. If so programmed, the assertion of LOL with invoke Fastlock. Because Fastlock temporarily increases the loop BW by asynchronously inserting new filter parameters into the DSPLL's closed loop, there may be transients at the clock outputs when Fastlock is either entered or exited. For this reason, it is suggested that automatic entry into Fastlock be disabled by writing a zero to FASTLOCK\_AUTO\_EN at 0x52B[0] whenever a clock switch might occur. For more details on hitless switching please refer to AN1057: Hitless Switching using Si534x/8x Devices.

#### 5.2.5 Glitchless Input Switching

The DSPLL has the ability to switch between two input clock frequencies that are up to ±500 ppm apart. The DSPLL will pull-in to the new frequency at a rate determined by the DSPLL loop bandwidth. The DSPLL loop bandwidth is set using registers 0x0508–0x050D. Note that if "Fastlock" is enabled then the DSPLL will pull-in to the new frequency using the Fastlock Loop Bandwidth. Depending on the LOL configuration settings, the loss of lock (LOL) indicator may assert while the DSPLL is pulling-in to the new clock frequency. There will never be output runt pulses generated at the output during the transition.

#### 5.2.6 External Clock Switching

External clock switches should be avoided because the Si5342/4/5 has no way of knowing when a clock switch will or has occurred. Because of this, neither the phase buildout engine or the ramp logic can be used. If expansion beyond the four clock inputs is an important issue, please see AN1111: Si534x/8x Input Clock Expander which describes how an external FPGA can be used for this purpose.

#### 5.2.7 Synchronizing to Gapped Input Clocks

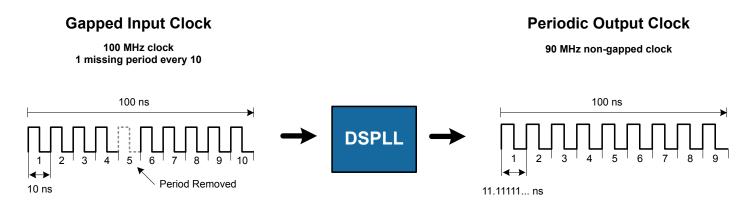

The DSPLL supports locking to an input clock that has missing clock periods. This is also referred to as a gapped clock. The purpose of gapped clocking is to modulate the frequency of a periodic clock by selectively removing some of its cycles. Gapping a clock severely increases its jitter so a phase-locked loop with high jitter tolerance and low loop bandwidth is required to produce a low-jitter, truly periodic clock. The resulting output will be a periodic non-gapped clock with an average frequency of the input with its missing cycles. For example, an input clock of 100 MHz with one cycle removed every 10 cycles will result in a 90 MHz periodic non-gapped output clock. A valid gapped clock input must have a minimum frequency of 10 MHz with a maximum of 2 missing cycles out of every 8.

When properly configured, locking to a gapped clock will not trigger the LOS, OOF, and LOL fault monitors. Clock switching between gapped clocks may violate the hitless switching specification for a maximum phase transient, when the switch occurs during a gap in either input clocks. Figure 5.2 Generating an Averaged Non Gapped Output Frequency from a Gapped Input on page 23 shows a 100 MHz clock with one cycle removed every 10 cycles, which results in a 90 MHz periodic non-gapped output clock.

Figure 5.2. Generating an Averaged Non Gapped Output Frequency from a Gapped Input

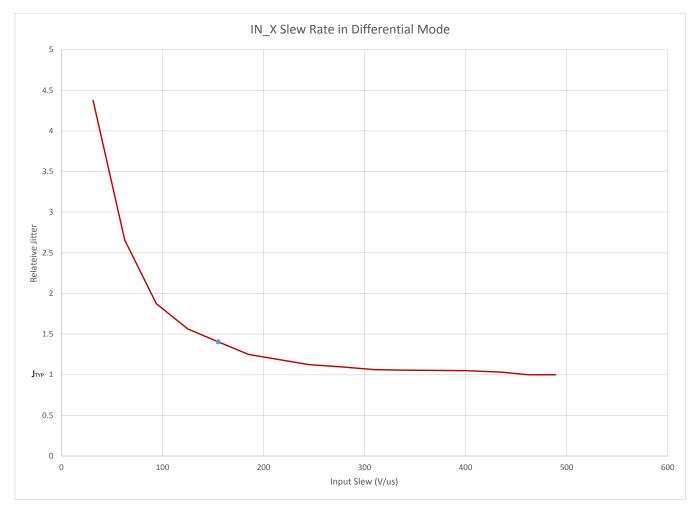

#### 5.2.8 Rise Time Considerations

It is well known that slow rise time signals with low slew rates are a cause of increased jitter. In spite of the fact that the low loop BW of the Si5342/44/45 will attenuate a good portion of the jitter that is associated with a slow rise time clock input, if the slew rate is low enough, the output jitter will increase. The following figure shows the effect of a low slew rate on RMS jitter for a differential clock input. The figure shows the relative increase in the amount of RMS jitter due to slow rise time and is not intended to show absolute jitter values.

Figure 5.3. Effect of Low Slew Rate on RMS Jitter

#### 5.3 Fault Monitoring

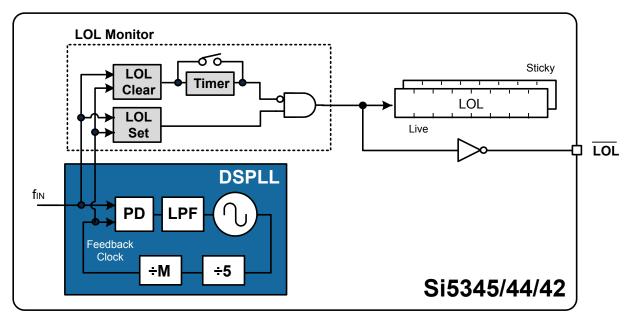

The four clocks (IN0, IN1, IN2, IN3/FB\_IN) are monitored for loss of signal (LOS) and out-of-frequency (OOF). Note that the reference at the XA/XB pins is also monitored for LOS since it provides a critical reference clock for the DSPLL. There is also a Loss of Lock (LOL) indicator asserted when the DSPLL loses synchronization within the feedback loop. Figure 5.4 Si5342/44/45 Fault Monitors on page 25 shows the fault monitors for each input path going into the DSPLL, which includes the crystal input as well as IN0-3.

Figure 5.4. Si5342/44/45 Fault Monitors

#### 5.3.1 Input Loss of Signal (LOS) Fault Detection

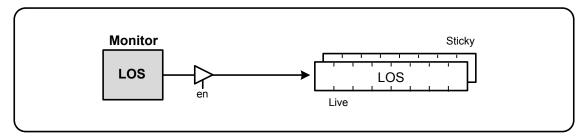

The loss of signal monitor measures the period of each input clock cycle to detect phase irregularities or missing clock edges. Each of the input LOS circuits has its own programmable sensitivity which allows ignoring missing edges or intermittent errors. Loss of signal sensitivity is configurable using the ClockBuilder Pro utility. The LOS status for each of the monitors is accessible by reading a status register. The live LOS register always displays the current LOS state and a sticky register when set, always stays asserted until cleared by the user.

Figure 5.5. LOS Status Indicators

A LOS monitor is also available to ensure that the external crystal or reference clock is valid. By default the output clocks are disabled when LOSXAXB is detected. This feature can be disabled such that the device will continue to produce output clocks even when LOSXAXB is detected. Single-ended inputs must be connected to the XA input pin with the XB pin terminated properly for LOSXAXB to function correctly. The table below lists the loss of signal status indicators and fault monitoring control registers.

Table 5.7. Loss of Signal Status Monitoring and Control Registers

| Register Name | Hex Address<br>[Bit Field]  | Function                                                                                                                                                                                              |  |

|---------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LOS           | 0x000D[3:0]                 | LOS status monitor for IN3 (bit3), IN2 (bit2), IN1(bit1), IN0 (bit0) indicates if a valid clock is detected. A set bit indicates the input is LOS.                                                    |  |

| SYSINCAL      | 0x000C[0]                   | Asserted when in calibration                                                                                                                                                                          |  |

| LOSXAXB       | 0x000C[1]                   | LOS status monitor for the STAL or REFCLK at the XA/XB pins                                                                                                                                           |  |

| LOS_FLG       | 0x0012[3:0]                 | LOS status monitor sticky bits for IN3, IN2, IN1, IN0. Sticky bits will remain asserted when a LOS event occurs until manually cleared. Writing zero to the bit will clear it.                        |  |

| SYSINCAL_FLG  | 0x0011[0]                   | SYSINCAL sticky bit. Sticky bits will remain asserted until written with a zero to clear.                                                                                                             |  |

| LOSXAXB_FLG   | 0x0011[1]                   | LOS status monitor sticky bits for XAXB. Sticky bits will remain asserted when a LOS event occurs until cleared. Writing zero to the bit will clear it.                                               |  |

| LOS_EN        | 0x002C[3:0]                 | LOS monitor enable for IN3, IN2, IN1, IN0. Allows disabling the monitor if unused.                                                                                                                    |  |

|               |                             | 0: Disable LOS Detection                                                                                                                                                                              |  |

|               |                             | 1: Enable LOS Detection (default)                                                                                                                                                                     |  |

| LOSXAXB_DIS   | 0x002C[4]                   | Enable LOS detection on the XAXB inputs.                                                                                                                                                              |  |

|               |                             | 0: Enable LOS Detection (default)                                                                                                                                                                     |  |

|               |                             | 1: Disable LOS Detection                                                                                                                                                                              |  |

| LOS_TRIG_THR  | 0x002E[7:0]-0<br>x0035[7:0] | Sets the LOS trigger threshold and clear sensitivity for IN3, IN2, IN1, IN0. These 16- bit values are determined by ClockBuilder Pro                                                                  |  |

| LOS_CLR_THR   | 0x0036[7:0]-0<br>x003D[7:0] |                                                                                                                                                                                                       |  |

| LOS_VAL_TIME  | 0x002D[7:0]                 | LOS clear validation time for IN3, IN2, IN1, IN0. This sets the time that an input must have a valid clock before the LOS condition is cleared. Settings of 2ms, 100ms, 200ms, and 1 s are available. |  |

| LOS_INTR_MSK  | 0x0018[3:0]                 | This is the LOS interrupt mask, which can be cleared to trigger an interrupt on the INTR pin if an LOS occurs for IN0-3.                                                                              |  |

#### 5.3.2 Out of Frequency (OOF) Fault Detection

Each input clock is monitored for frequency accuracy with respect to an OOF reference which it considers as its 0 ppm reference. This OOF reference can be selected as either:

XA/XB pins

Any input clock (IN0, IN1, IN2, IN3)

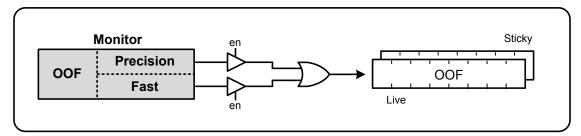

The final OOF status is determined by the combination of both a precise OOF monitor and a fast OOF monitor as shown in Figure 9. An option to disable either monitor is also available. The live OOF register always displays the current OOF state and its sticky register bit stays asserted until cleared.

Figure 5.6. OOF Status Indicator

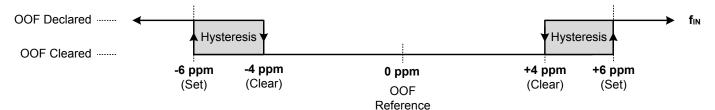

The Precision OOF monitor circuit measures the frequency of all input clocks to within up to ±0.0625 ppm accuracy with respect to the selected OOF frequency reference. A valid input clock frequency is one that remains within the register-programmable OOF frequency range of from ±0.0625 ppm to ±512 ppm in steps of 1/16 ppm. A configurable amount of hysteresis is also available to prevent the OOF status from toggling at the failure boundary. An example is shown in the figure below. In this case, the OOF monitor is configured with a valid frequency range of ±6 ppm and with 2 ppm of hysteresis. An option to use one of the input pins (IN0–IN3) as the 0 ppm OOF reference instead of the XAXB pins is available. These options are all register configurable.

Figure 5.7. Example of Precise OOF Monitor Assertion and De-assertion Triggers

Table 5.8 Out-of-Frequency Status Monitoring and Control Registers on page 27 lists the OOF monitoring and control registers. Because the precision OOF monitor needs to provide 1/16 ppm of frequency measurement accuracy, it must measure the monitored input clock frequencies over a relatively long period of time. This may be too slow to detect an input clock that is quickly ramping in frequency. An additional level of OOF monitoring called the Fast OOF monitor runs in parallel with the precision OOF monitors to quickly detect a ramping input frequency. The Fast OOF responds more quickly and has larger thresholds.

| Register Name | Hex Address<br>[Bit Field] | Function                                                                                                                                                              |  |

|---------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OOF           | 0x000D[7:4]                | OOF status monitor for IN3, IN2, IN1, IN0. Indicates if a valid clock is detected or if a OOF condition is detected.                                                  |  |

| OOF_FLG       | 0x0012[7:4]                | OOF status monitor sticky bits for IN3, IN2, IN1, IN0. Stick bits will remain asserted when an OOF event occurs until cleared. Writing zero to the bit will clear it. |  |

| OOF_INTR_MSK  | 0x0018[7:4]                | Masks OOF from generating INTR interrupt for IN3 – IN0.                                                                                                               |  |

|               |                            | 0: Allow OOF interrupt (default)                                                                                                                                      |  |

|               |                            | 1: Mask (ignore) OOF for interrupt                                                                                                                                    |  |

| Register Name    | Hex Address<br>[Bit Field]  | Function                                                                                                                            |  |

|------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| OOF_REF_SEL      | 0x0040[2:0]                 | This selects the clock that the OOF monitors use as the 0 ppm reference. Selections are XA/XB, IN0, IN1, IN2, IN3. Default is XAXB. |  |

| OOF_EN           | 0x003F[3:0]                 | This allows to enable/disable the precision OOF monitor for IN3, IN2, IN1, IN0                                                      |  |

| FAST_OOF_EN      | 0x003F[7:4]                 | This allows to enable/disable the fast OOF monitor for IN3, IN2, IN1, IN0                                                           |  |

| OOF_SET_THR      | 0x0046[7:0]-0x0<br>049[7:0] | OOF Set threshold. Range is up to ±500 ppm in steps of 1/16 ppm                                                                     |  |

| OOF_CLR_THR      | 0x004A[7:0]-0x0<br>04D[7:0] | 0 OOF Clear threshold. Range is up to ±500 ppm in steps of 1/16 ppm                                                                 |  |

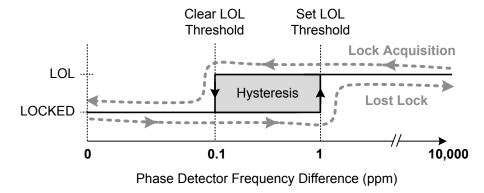

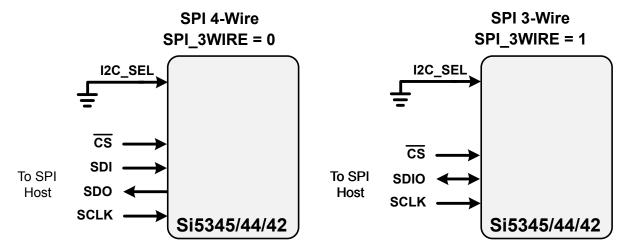

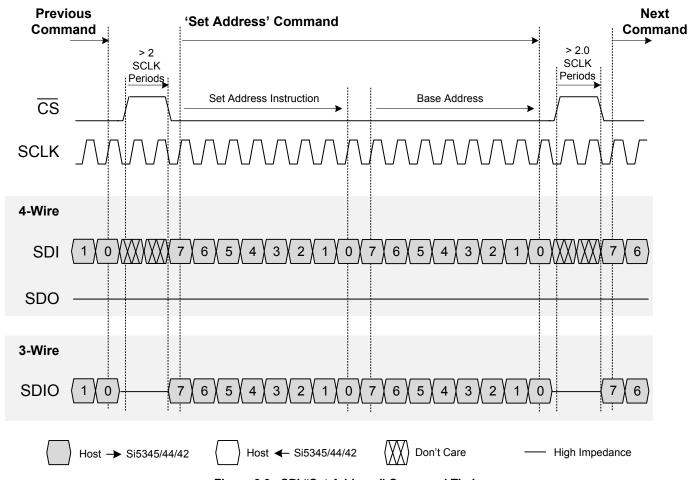

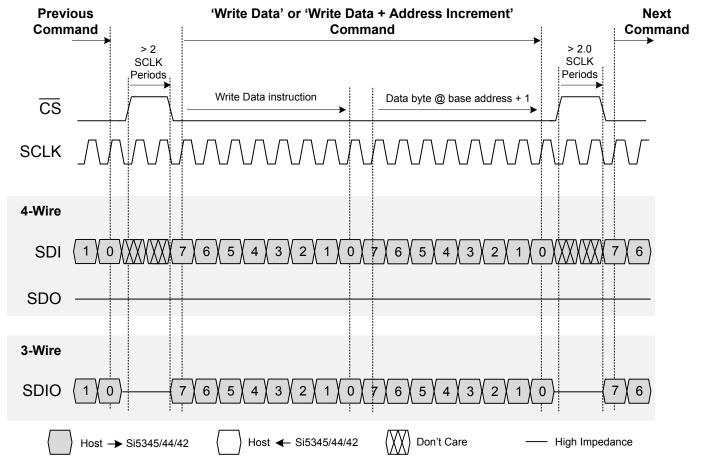

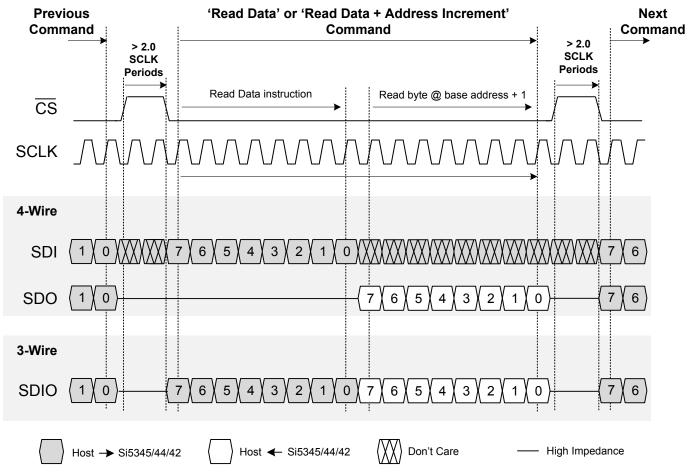

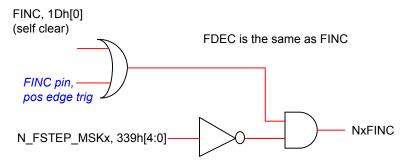

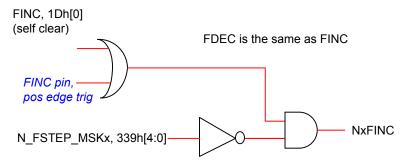

| FAST_OOF_SET_THR | 0x0051[7:0]-0x0<br>054[7:0] | Determines the fast OOF alarm set threshold for IN3, IN2, IN1, IN0.                                                                 |  |